| 2022年04月23日 | 更新 |

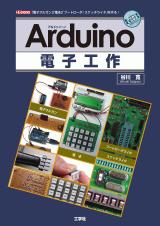

図21に示す様に、2つのDフリップフロップを縦続に接続(一方の出力をもう一方の入力に接続することでカスケード接続ともいいます)して、両方のDフリップフロップに共通のクロック信号を与えた場合を考えます。

この回路では、D端子に信号を加えると、一つ目のDフリップフロップであるFF1がD信号をCLK信号の立ち上がりで読み取ります。そうして得られたQ1信号を2つ目のフリップフロップであるFF2がCLK信号の立ち上がりで取り込むと、得られるQ2信号は、Q1信号より1クロック遅れた信号になります。

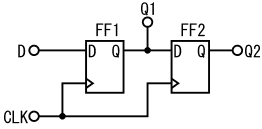

図21の回路のタイミングチャートの例を図22に示します。

このタイミングチャートの赤い楕円で囲んだ部分を見ると、CLK信号がLからHに立ち上がると同時に、Q1信号がHからLに立ち下がっている様に見えます。これでは、CLK信号が立ち上がった瞬間のQ1信号の論理が決まらず、FF2の動作が不確定になりそうな気がします。

しかし、図23に示す様に、赤い楕円で囲んだ部分を時間軸方向に拡大してみると、様子が変わってきます。

フリップフロップFF1は、CLK信号の立ち上がり時のD信号の論理を読み取り、それをQ1信号として出力しますが、実際にD信号を読み取ってから、Q1信号にそれが反映されるまでには、わずかですが時間がかかります。(その時間は、使うDフリップフロップによって変わりますが、高速CMOSデバイスを用いる場合はおおむね数nsです) そのため、CLK信号の立ち上がりの瞬間にD信号がLであるのを読み取ってから、数ns経過して、Q1信号がHからLに立ち下がります。

この結果、CLK信号が立ち上がる瞬間のQ1信号はHとなります。そのため、CLK信号が立ち上がった後のQ2信号もHとなります。

この様に、DフリップフロップのD信号として、CLK信号の立ち上がりに同期して変化する信号を入力した場合、D信号がCLK信号に対してわずかな時間遅れて変化するため、Dフリップフロップは、D信号の変化前の状態を読み取ります。

注:この議論を厳密に行うためには、伝搬遅延時間、セットアップ時間、ホールド時間などについて説明する必要があるのですが、ここでは概念的な説明にとどめておきます。

この、Dフリップフロップを通るとクロック同期した信号を1クロック分遅らせる事の出来る性質を、積極的に応用した回路としては、シフトレジスタを用いた遅延回路やシリアル-パラレル変換回路が挙げられます。

Dフリップフロップを4つ縦続に接続して作った4ビットのシリアル-パラレル変換用シフトレジスタの回路図を図24に、またそのタイミングチャートの例を図25に示します。これらの図の詳しい説明は、この用語集のシリアル-パラレル変換回路の項目をご覧ください。

先に説明した様に、Dフリップフロップの電源投入直後の記憶内容(Q信号)は不定です。よって、下手に同期回路(Dフリップフロップをたくさん含む回路)を設計すると、その動作が、各Dフリップフロップの初期値に影響を受け、電源を投入するたびに振る舞いが変わる恐れがあります。

もし、電源投入直後の各Dフリップフロップの状態を、それぞれにLあるいはHの好きな方に固定できれば、設計によらず毎回同じ動作をする事が保証できて、安心です。

こういう時は、電源投入直後のDフリップフロップの状態を指定するための、非同期クリア端子や非同期プリセット端子が付いたDフリップフロップを使うのが便利です。

他の入力端子の真理値や、Dフリップフロップが記憶していた真理値にかかわらず、Dフリップフロップに強制的にLを記憶させるための入力端子を、非同期クリア端子と呼びます。

図26に、非同期クリア端子のあるDフリップフロップの回路記号を示します。また比較のために、非同期クリア端子のないフリップフロップの回路記号(図7)を再掲します。

図26の記号では、図7の記号にCLR端子が追加されています。CLR端子は下に書くことが多い様です。

このCLR端子にHが入力されると、他の端子の状態にかかわらず、Q信号はLになります。そして、CLR端子にHが入力され続けている間はQ信号はLを維持します。CLR端子にLが入力されると、図7のフリップフロップと同様の動作をします。

注:非同期クリア端子は、非同期リセット端子と呼ばれることもあります。またCLR端子は、教科書によってはCLEAR端子、C端子、R端子、RES端子、RESET端子等と書いてある場合もあります。

この動作を真理値表で表すと、表5の様になります。

| 入力信号 | 出力信号 | 動作 | |||

|---|---|---|---|---|---|

| CLR | CLK | D | Q | Q | |

| H | X | X | L | H | 非同期クリア |

| L | L | X | q | q | 保持 |

| L | H | X | q | q | |

| L | ↓ | X | q | q | |

| L | ↑ | L | L | H | 読み取り |

| L | ↑ | H | H | L | |

注:表5における"X"、"↑"、"↓"、"q"、"q"の記号の意味は、表2と同様です。

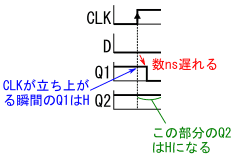

非同期クリア端子付きのDフリップフロップのタイミングチャートの例を図27に示します。

このタイミングチャートから、CLR端子がHの期間に、CLK信号の立ち上がりのタイミングに関係なく、Q信号がLになる様子が分かります。

なお、非同期クリア端子を非同期リセット端子とも呼ぶ事は先に説明しましたが、電源投入時のフリップフロップの不定状態を解消するために非同期クリア端子を使う場合、あるいは(基板上のリセットボタンを押すなどして)回路全体を初期状態に戻すために非同期クリア端子を使う場合に「フリップフロップをリセットする」という表現をし、逆に、通常の回路の動作の一環として、(全てのフリップフロップではなく特定のフリップフロップの)非同期クリア端子でQ信号をLにする場合を「フリップフロップをクリアする」と表現して、区別する場合があります。

参考:同期回路を設計する場合は、回路の初期化(電源投入時の不定状態の解消および回路動作中に回路全体を初期状態に戻す処理)にのみ非同期クリア端子を使い、通常の回路の動作の一環としては非同期クリア端子を使う事を禁止する場合が多いです。これは、通常の回路動作の一環として、不用意に非同期クリア端子を使うと、非同期クリア信号にハザードが発生し、予期せぬタイミングでフリップフロップがクリアされる危険があるためです。

他の入力端子の真理値や、Dフリップフロップが記憶していた真理値にかかわらず、Dフリップフロップに強制的にHを記憶させるための入力端子を、非同期プリセット端子と呼びます。非同期クリア端子はDフリップフロップに強制的にLを記憶させる端子でしたので、非同期プリセット端子は、非同期クリア端子と逆の働きをする端子という事になります。

非同期プリセット端子付きのDフリップフロップの回路記号を図28に示します。

この図のPREと書いてある端子が非同期プリセット端子です。非同期プリセット端子は、上側に書く場合が多い様です。

注:非同期プリセット端子は、非同期セット端子と呼ばれる場合もあります。教科書によっては、PRE端子はPRESET端子、P端子、SET端子、S端子等と書いてある場合もあります。

非同期プリセット端子付きのDフリップフロップの真理値表を表6に示します。

| 入力信号 | 出力信号 | 動作 | |||

|---|---|---|---|---|---|

| PRE | CLK | D | Q | Q | |

| H | X | X | H | L | 非同期プリセット |

| L | L | X | q | q | 保持 |

| L | H | X | q | q | |

| L | ↓ | X | q | q | |

| L | ↑ | L | L | H | 読み取り |

| L | ↑ | H | H | L | |

注:表6における"X"、"↑"、"↓"、"q"、"q"の記号の意味は、表2と同様です。

非同期プリセット端子付きのフリップフロップのタイミングチャートの例を図29に示します。

非同期プリセット端子を非同期セット端子と呼ぶ場合もある事は先に説明しましたが、回路の初期化のために非同期プリセット端子でHを書き込む場合を「フリップフロップをプリセット」すると呼び、回路の通常の動作の一環として非同期プリセット端子でHを書き込む場合を「フリップフロップをセットする」と呼んで、区別する場合もあります。

参考:プリセットは、「あらかじめセットしておく」という意味の言葉です。

非同期クリア端子と非同期プリセット端子の両方があるDフリップフロップも存在します。その回路記号を図30に、真理値表を表7に示します。

| 入力信号 | 出力信号 | 動作 | ||||

|---|---|---|---|---|---|---|

| CLR | PRE | CLK | D | Q | Q | |

| H | L | X | X | L | H | 非同期クリア |

| L | H | X | X | H | L | 非同期プリセット |

| H | H | X | X | U | U | 禁止 |

| L | L | L | X | q | q | 保持 |

| L | L | H | X | q | q | |

| L | L | ↓ | X | q | q | |

| L | L | ↑ | L | L | H | 読み取り |

| L | L | ↑ | H | H | L | |

注:表7における"X"、"↑"、"↓"、"q"、"q"の記号の意味は、表2と同様です。"U"は未定義を表します。

表7の真理値表から分かるように、CLR信号がHでPRE信号がLなら、Q信号はLでQ信号はHになります。(非同期クリア)

また、CLR信号がLでPRE信号がHなら、Q信号はHでQ信号はLになります。(非同期プリセット)

また、CLR信号とPRE信号が両方Lなら、非同期クリア端子や非同期プリセット端子がないDフリップフロップ(図7)と同様の動作になります。

注意しなければならないのは、CLR信号とPRE信号が両方ともHの場合です。CLR信号はDフリップフロップに強制的にLを記憶させる信号で、PRE信号はDフリップフロップに強制的にHを記憶させる信号なので、両方を同時にHにすると、矛盾が発生します。そのため、この時のQ信号およびQ信号は未定義になります。

未定義というのは、Lになるか、Hになるかが決まっていないという事です。実際にはLまたはHのいずれかが出力されるのですが、Lが出力される事、あるいはHが出力される事を期待して回路設計を行ってはいけません。

参考1:FPGAやASICの設計において非同期クリア端子と非同期プリセット端子のあるDフリップフロップを使用する場合、HDL(ハードウェア記述言語)でDフリップフロップをどう記述するかで、CLR信号とPRE信号の両方がHの時の挙動が決まります。CLR信号とPRE信号の両方がHの時に出力が未定義になるような記述法もありますが、その場合は、HDLのコンパイラが、回路規模が最小になるようにCLR信号とPRE信号の両方がHの時の出力状態を定めます。

参考2:74HCシリーズなどの汎用ロジックICで非同期クリア端子と非同期プリセット端子のあるDフリップフロップを使用する場合、使用するICのデータシートで、CLR信号とPRE信号の両方がHの時の出力状態が定義されています。例えば74HC74は、負論理の非同期クリア端子と負論理の非同期プリセット端子の両方があるDフリップフロップが2個、1つのパッケージに収められたICです。74HC74の場合、CLR信号とPRE信号の両方がLになる場合は、Q信号とQ信号の両方がHになると定義されています。

通常、出力が未定義になるCLR信号とPRE信号の両方がHになる状態にする事は禁止されています。

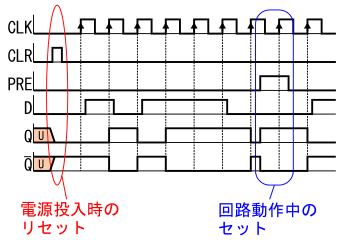

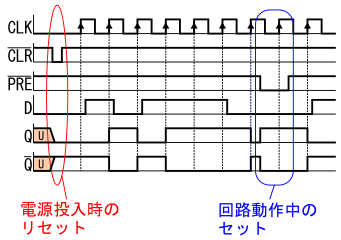

非同期クリア端子と非同期プリセット端子の両方があるDフリップフロップタイミングチャートの例を、図31に示します。

CLR信号とPRE信号を同時にHにする事は禁止されているので、そうならないような信号を入力した例を示しています。

市販されている汎用ロジックICでは、非同期クリア端子や非同期プリセット端子が負論理になっている場合が多くあります。

負論理の非同期クリア端子と負論理の非同期プリセット端子のあるフリップフロップ回路の回路記号を図32に、真理値表を表8に、タイミングチャートの例を図33に示します。

| 入力信号 | 出力信号 | 動作 | ||||

|---|---|---|---|---|---|---|

| CLR | PRE | CLK | D | Q | Q | |

| L | H | X | X | L | H | 非同期クリア |

| H | L | X | X | H | L | 非同期プリセット |

| L | L | X | X | U | U | 禁止 |

| H | H | L | X | q | q | 保持 |

| H | H | H | X | q | q | |

| H | H | ↓ | X | q | q | |

| H | H | ↑ | L | L | H | 読み取り |

| H | H | ↑ | H | H | L | |

注:表8における"X"、"↑"、"↓"、"q"、"q"、"U"の記号の意味は、表7と同様です。

CLR信号とPRE信号を同時にLにする事は禁止されているので、そうならないような信号を入力した例を示しています。