| 2022年04月23日 | 更新 |

Dフリップフロップは、1ビットの情報を記憶する事のできる論理回路で、同期回路を設計する場合に中心的な役割を果たす回路要素です。

DフリップフロップにはD端子およびCLK端子の2つの入力端子と、Q端子の1つの出力端子を必ず備えています。また、さらに多くの端子を備えたDフリップフロップもあります。

D端子に記憶させたい真理値を入力した状態で、CLK信号を立ち上げる(LからHに遷移させる)と、D端子の真理値をDフリップフロップが記憶し、それをQ端子に出力します。Q端子の出力は、次にCLK信号が立ち上がり、記憶内容が更新されるまでは変化しません。

注:後述する様に、CLK信号の立ち下がりのタイミングでD信号を取り込むDフリップフロップも存在します。

大規模な論理回路を設計する場合、組み合わせ回路のみで構成される非同期回路の形で設計すると、信号の変化のタイミングの管理が大変になり、それがうまく管理できないと、波形にハザード)(波形割れ)が生じるなどして、回路が誤作動してしまいます。

参考:例えばAND回路やOR回路など、その時の入力信号の真理値のみで出力信号の真理値が決まる回路を組み合わせ回路といいます。Dフリップフロップは、出力信号の真理値が、その時の入力信号の真理値だけではなく、過去の入力信号の影響を受けますので、組み合わせ回路ではありません。Dフリップフロップの様に、出力信号の状態が、現在だけではなく過去の入力信号の影響を受ける論理回路を順序回路といいます。

複数のDフリップフロップの間に小規模の組み合わせ回路を挟んだ回路構成で、全てのDフリップフロップに共通のクロック信号(CLK信号)を入力する論理回路をクロック同期回路(あるいは単に同期回路)といいます。同期回路の場合、たとえ組み合わせ回路でハザードが発生しても、ハザードが終わった後の真理値をDフリップフロップに取り込む事により、ハザードの弊害を表面化させない事ができるため、回路設計が簡略化し、大規模の論理回路を設計した場合でも、誤作動の発生しない、信頼性の高い回路を作る事ができます。この利点から、現在設計される大規模の論理回路は、ほとんどが同期回路として設計されています。

この様に、大規模の論理回路にはDフリップフロップが数多く使われているため、その動作の理解は、論理回路を理解する上で必要不可欠といえます。

なお、Dフリップフロップの表記は、DFF、D-FF、あるいはD-F/Fなどと省略される場合があります。

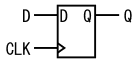

Dフリップフロップと呼ばれる回路にはいくつかのバリエーションがありますが、図1に示す様に、D端子とCLK端子の2つの入力端子と、Q端子の1つの出力端子を備えるDフリップフロップが最小構成で、最も基本的なDフリップフロップといえます。

D信号とQ信号はその時の真理値に意味がある、普通の信号ですが、CLK信号は、立ち上がりのタイミングに意味がある、少し特殊な信号です。この様な、立ち上がり(あるいは立ち下がり)のタイミングのみに意味がある信号を、普通クロック信号(あるいは単にクロック)とかストローブ信号と呼びます。クロック信号の名称は、常時同じ周波数で信号が出ている場合に使う事が多く、ストローブ信号の名称は、必要な時のみにパルスが出る場合に使う事が多いですが、必ずその様に名称が使い分けられる訳ではありません。このページでは、CLK信号の事をクロック信号と呼びます。

注1:CLK端子は、教科書によりCK端子、C端子、ST端子等と書いてある場合があります。

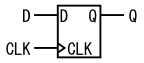

注2:CLK端子についている三角印は、クロック信号である事を示します。教科書によっては、図2に示す様に三角印の右に"CLK"と信号名が書いてある事があります。このページでは、わざわざ"CLK"と書かなくても三角印だけでクロック信号であると判断できるとの立場から、回路記号には"CLK"とは書かない事にします。

この図の様に回路記号中に"CLK"と明記する方が、より信号の意味が明瞭になります。しかしDフリップフロップの場合は受け取るクロック信号が1つですので、三角印があれば、その右に"CLK"と書かなくても、それがCLK信号である事は理解できます。大規模な回路で、受け取るクロック信号が複数ある場合は、三角印だけではなく、必ず信号名を書く必要があります。

注3:クロック端子に三角印を付けるのは、単に、比較的に普及している習慣に過ぎません。よって、教科書により、図3の様にクロック端子に三角印を書いていない回路記号を使っている場合もあります。

Dフリップフロップの各端子の名称と意味は、表1の様になります。

| 名称 | 働き |

|---|---|

| CLK | クロックの入力信号です。この信号の立ち上がる瞬間のD端子への入力を、Dフリップフロップが記憶します。 |

| D | 入力信号です。CLK信号が立ち上がる瞬間に、この信号をフリップフロップが取り込んで記憶します。 |

| Q | 出力信号です。Dフリップフロップが記憶している真理値を出力します。 |

Dフリップフロップの真理値表は、表2の様になります。

| 入力信号 | 出力信号 | 動作 | |

|---|---|---|---|

| CLK | D | Q | |

| L | X | q | 保持 |

| H | X | q | |

| ↓ | X | q | |

| ↑ | L | L | 読み取り |

| ↑ | H | H | |

ただし、表2には次の記号を使っています。

この表から分かるように、CLK信号がL、H、または立ち下がりの3つの状態のいずれかにある時は、D信号の状態にかかわらず、Q信号には直前のQ信号の値が出ます。つまり、Q信号の真理値が保持されます。

またCLK信号が立ち上がる瞬間には、Q信号には、その時のD信号と同じ値が出ます。つまり、CLK信号の立ち上がりのタイミングでフリップフロップはD信号を読み取る事になります。

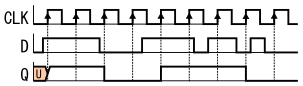

この動作をタイミングチャートで確認してみましょう。図4にDフリップフロップのタイミングチャートの例を示します。

ポジティブエッジトリガという用語は、回路がクロック信号の立ち上がりに同期して動作する事を意味します。詳しくは後述します。

電源投入直後のDフリップフロップが記憶する真理値は不定です。図の中のUは、不定(LかHか分からない状態)を表します。

このタイミングチャートで特徴的なのは、最初のCLK信号の立ち上がりまで、Q信号がUになっている事です。このUは「不定」(LかHか分からない状態)を表します。

表2の真理値表を見ると、CLKが立ち上がる瞬間にD信号の真理値がQ信号に反映され、CLKが立ち上がるタイミング以外では、Q信号の真理値が保持される事が分かります。

しかし、電源が入っていない時間にはCLK信号の真理値というのが定義できないので、たとえ電源投入のタイミングでCLK信号がHになる場合でも、立ち上がった(LからHに遷移した)とは言えないのです。(逆にCLK信号が立ち上がらなかったとも言えません) 仮に電源投入時にCLK信号が立ち上がらないと考えると、Q信号は直前の値を保持するはずですが、電源投入直前のQ信号の真理値は、やはり定義できません。

実際にDフリップフロップに電源を投入するとどうなるかというと、個体によっては電源投入直後に必ずQ信号がLになり、また別の個体では電源投入直後に必ずQ信号がHになり、さらに別の個体では電源を投入するたびに、Q信号がLになったりHになったりします。この様に、最初にCLK信号を立ち上げるまでは、フリップフロップが記憶している真理値(Q信号に出てくる真理値)は予測不能なのです。

最初にCLK信号が立ち上がった瞬間にフリップフロップはD信号を読み込み、フリップフロップの記憶する真理値が確定します。

それ以降は、CLK信号の立ち上がりの瞬間にD信号を読み込んでQ信号に反映し、次のCLK信号の立ち上がりの瞬間までQ信号の値を保持するという動作を繰り返します。

真理値表やタイミングチャートから分かるように、Dフリップフロップの出力信号(Q信号)は、CLK信号の立ち上がりのタイミングにのみ変化します。この様にクロック信号の立ち上がり(あるいは立ち下がり)のタイミングに合わせて出力信号の状態が変わる回路動作の事をクロック同期といいます。

クロック同期する回路の事をクロック同期回路(あるいは単に同期回路)といいますが、同期回路には必ず、Dフリップフロップや、それに類する回路が内蔵されています。「それに類する回路」は、必ずDフリップフロップと、AND、OR、NOTなどの基本的なゲート素子の組み合わせで同じ機能を実現できますから、全ての同期回路には、「等価的に」Dフリップフロップを内蔵しているという表現もできます。

参考:「それに類する回路」というのは、具体的にはTフリップフロップやJKフリップフロップなどの事を指します

同期回路を、クロック信号の立ち上がりあるいは立ち下がりのタイミングに合わせて出力状態が変わる回路だと説明しましたが、Dフリップフロップの中にも、クロック信号の立ち下がりのタイミングに合わせてQ信号の値が変化するものもあります。この様なDフリップフロップを、ネガティブエッジトリガのDフリップフロップといいます。

それに対し、前節で紹介した様に、クロック信号の立ち上がりのタイミングに合わせてQ信号の値が変化するDフリップフロップを、ポジティブエッジトリガのDフリップフロップといいます。

参考:波形の立ち上がりの事をポジティブエッジ、波形の立ち下がりの事をネガティブエッジといいます。トリガとは元々銃の引き金の事ですが、電子回路においては、何かの信号の変化を合図に回路が動作する事を意味します。

ネガティブエッジトリガのDフリップフロップの回路記号を図5に、真理値表を表3に示します。

| 入力信号 | 出力信号 | 動作 | |

|---|---|---|---|

| CLK | D | Q | |

| L | X | q | 保持 |

| H | X | q | |

| ↑ | X | q | |

| ↓ | L | L | 読み取り |

| ↓ | H | H | |

注:表3における"X"、"↑"、"↓"および"q"の記号の意味は、表2と同様です。

図5に示す様に、ネガティブエッジトリガのDフリップフロップの回路図記号の入力端子の部分には、通常、負論理を表す〇印を付けます。信号名には、CLKと、負論理を表す上線を付ける事が多いですが、上線を付けない場合もあります。

表2の真理値表を元に作成した、ネガティブエッジトリガのDフリップフロップのタイミングチャートの例を図6に示します。比較のために、図4(ポジティブエッジトリガのDフリップフロップのタイミングチャート)を再掲します。

DフリップフロップがQ信号を生成する際には、回路構成上の問題で、必ずQ信号を論理反転したQ信号も生成します。(理由は後述) Q信号と同時にQ信号も出力するDフリップフロップの回路記号を図7に示します。

Dフリップフロップ内部では、Q信号と同時にQ信号も生成しているので、この図7のDフリップフロップが、図1に示したQ信号だけを出力するDフリップフロップよりも基本的なDフリップフロップだと考える場合もあります。

ただ、Q信号のない方が信号線が少なくて理解しやすいですし、74HC174など、Q端子を省略したDフリップフロップのICも製品化されているため、このページでは図1のDフリップフロップが基本形で、図4はQ信号を追加した発展形だと紹介しておきます。

図7のDフリップフロップの真理値表を表4に、タイミングチャートの例を図8に示します。

| 入力信号 | 出力信号 | 動作 | ||

|---|---|---|---|---|

| CLK | D | Q | Q | |

| L | X | q | q | 保持 |

| H | X | q | q | |

| ↓ | X | q | q | |

| ↑ | L | L | H | 読み取り |

| ↑ | H | H | L | |

注:表4における"X"、"↑"、"↓"および"q"の記号の意味は、表2と同様です。"q"は、直前のQ信号の値の論理否定(NOT)を表します。

図の中のUは、不定(LかHか分からない状態)を表します。

このタイミングチャートから、Q信号とQ信号の真理値が互いに論理反転している事が分かります。

最初のCLK信号の立ち上がりまでは、Q信号がHになるかLになるかは予測できませんが、起動直後の短時間の不安定な時間(ns~μsオーダーか?)を除いて、Q信号、Q信号の真理値は互いに論理反転しています。(言い換えると、Uと書いてある領域でも、Q信号とQ信号が同じ真理値のまま安定状態になる事はありません)

「ボタンが押された」、「起動後一定の時間が経過した」、「センサが異常を検出した」など、何かが起こった時や、何かをこれからしなければならない等の状況でHになり、それらの条件が成立しない時にはLになる信号を、正論理の信号といいます。逆に、何かが起こった時や、何かをこれからしなければならない等の状況でLになり、それらの条件が成立しない時にはHになる信号を、負論理の信号といいます。

負論理の信号には、信号名に上線を付けて、負論理である事を示す習慣になっています。

例えば、平時にはLになっていて、温度センサが異常に高い温度を検出した際にHとなって警告する正論理の信号には、HOTの様な信号名を付けるでしょう。逆に、平時にはHになっていて、異常に高い温度になったらLとなって警告する負論理の信号は、HOTと、上線を付けて表示する習慣になっています。(あくまで習慣ですので、上線を付けずにHOTという信号にして、それが負論理である事は、真理値表やタイミングチャートなどで説明するという考え方もあります)

回路図上の表記に関して言えば、負論理の端子には〇印を付ける習慣があります。

例えば、AND回路の出力端子が負論理になったNAND回路は、図9の様にAND回路の出力端子に〇印を付けて表記するのはご存知でしょう。

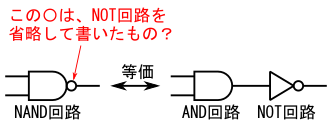

図9のNAND記号の〇印は、図10の様にNOT回路が省略表記されたものと考える事もできます。(おそらくそう解釈できるように〇印の記号を考えたのでしょう)

NAND回路の先端の〇印を取ってAND回路にし、その代わりにNOT回路を挿入すると、NAND回路と同じ働きをする回路になります。つまり、AND回路の外部につながったNOT回路を省略表記したのが、NAND回路の〇印だという解釈もできます。

NANDやNORなどの基本ゲート以外の論理回路でも、負論理の信号には端子に〇印を付ける習慣があります。これは習慣なので、〇印を付けないと間違いという訳ではありません。

注:NAND回路の記号の先端の〇をつけるかどうかは、任意という訳ではありません。必ず〇印を付ける必要があります。NAND回路の記号から〇を取ると、AND回路と区別できなくなります。また、図9に示したNAND回路の回路記号は、俗に"MIL記号"と呼ばれていて、MIL規格(アメリカ軍の物資の調達に使われる規格)のMIL-STD-806で規定されていた記号です。(MIL-STD-806は、現在では廃止されています) MIL-STD-806ではAND回路の記号の先端部に〇を書くのがNAND回路の回路記号だと決められていました。それだけではなく、AND回路の記号の直線部と半円の寸法の比やNAND回路記号の本体側(AND回路側)と先端の円の大きさの比など、寸法が細かく決まっていました。(このサイトの基本ゲートの記号は、細かい寸法比までMIL記号通りに書いている訳ではありません) 日本では、JIS規格に従った回路記号を使う事を推奨されているのですが、全ての論理ゲートを長方形で書き、長方形の中の文字で機能を区別するJIS記号は使い勝手が悪く、電子回路設計の実務の現場で使う人は、まずいません。MIL記号がデファクトスタンダードになっています。

先に、負論理の信号には上線の付いた信号名を付ける事と、負論理の信号線には端子部分に〇をつける事を説明しましたが、これらを組み合わせると、少し問題が生じます。

図7の回路記号は、その次に示す図11や図12の書き方でも書けてしまいます。

図7、図11、および図12の表記法には、見る人の立場によって、それぞれ図13~図15の様な批判が出ます。

図7、図11、および図12の回路記号は、いずれも実際に使われているのですが、一番よく使われているのは図12の回路記号の様です。しかし、このページでは図7の表記法で書く事にします。これは、筆者の好みによります。(図11の様に回路記号内部に書く信号名と実際の信号名が違うと、回路図CADを扱う場合に不便ですし、負論理の〇が付いていないと、一見して負論理だとわかりにくいからです)

なお、信号名を回路記号の中に書かない図9のNAND回路の様な場合は、負論理を示す方法が〇印を端子に付加する方法しかなく、信号名に上線を付ける事はできないため、図13~図15の様な問題は発生しません。

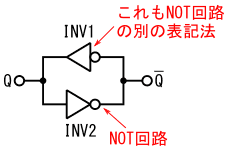

フリップフロップと呼ばれる回路は、Dフリップフロップ以外にも何種類かありますが、いずれも1ビットの情報を記憶する作用を持っています。そして、フリップフロップは、図16に示す様な、2つのNOT回路が環状に接続された回路の構造を1つ以上持っています。

この回路図にはINV1とINV2の2つのNOT回路があります。2つのNOT回路の回路記号が異なりますが、表記法が違うだけで、論理反転を行うという動作に差はありません。INV1の様に入力端子に〇印を付ける形式のNOT回路の記号は、負論理の信号を正論理の信号に変換するためのNOT回路の記号です。INV2の様に出力端子に〇印を付ける形式のNOT回路の記号は、正論理の信号を負論理の信号に変換するためのNOT回路の記号です。

図16では、INV1とINV2の2つのNOT回路が環状に接続されています。そしてINV1の出力をQ信号として、またINV2の出力をQ信号として外部に取り出して、状態を観察できるようにしてあります。

図16の回路には、図17と図18に示す2つの安定状態があります。

まず図17を見てください。この図ではQ信号がHになっています。INV2はこのHが入力されるとLを出力しますから、Q信号はLになります。今度はINV1にこのLが入力されてHが出力されますから、Q信号がHになります。

この様に、図17では、Q信号がHになる事を仮定したら、信号がINV2、INV1の順に通って、結果的にQ信号がまたHになりました。このため、電源が入っている限り、Q信号がHでQ信号がLの状態を維持するでしょう。よって、この状態は安定(時間的に信号が変化しない)といえます。

次に図18を見てください。この図ではQ信号がLになっています。INV2はこのLが入力されるとHを出力しますから、Q信号はHになります。今度はINV1にこのHが入力されてLが出力されますから、Q信号がLになります。

この様に、図18の状態も安定である事が分かりました。

図16の回路の様に、回路に安定な電圧分布が2つある状態の事を、双安定といいます。双安定な回路構成を組むことは、記憶素子を作る際に、基本的な事項となります。

参考:NOT回路を奇数個環状につなげた回路では、安定な状態にはなりません。例えば3個のNOT回路をつないだ図19(a)の様な回路を考えます。

この回路で、ある瞬間、(1)A信号がHだと仮定します。そうすると、A信号が入力されるNOT回路の働きにより、(2)B信号がLになります。さらにB信号が入力されるNOT回路の働きにより、(3)C信号がHになります。さらにC信号が入力されるNOT回路の働きにより、初期状態とは反対に、(4)A信号がLになります。初期状態が維持できませんから、この回路は不安定です。

この様に順に各所の真理値を計算していくと、タイミングチャートが図19(b)の様になる事が分かります。この様に、安定状態を持たない論理回路は発振するのです。

図19(a)の様に、NOT回路を奇数個、環状に接続して作った発振器は、リング発振器(リングオシレータ)と呼ばれます。リング発振器は、NOT回路が高速に動作するほど高い周波数で発振する性質を持っているので、新種のロジックデバイスを開発した時に、そのデバイスの速度の評価に使われます。

図16の回路は、Q信号がHの安定状態と、Q信号がLの定状態を持ちます。ここで、Q信号がLの安定状態になっている事を、「フリップフロップがHを記憶している」と呼ぶことにします。同様に、Q信号がLの安定状態になっている事を、「フリップフロップがLを記憶している」と呼ぶ事ににします。

フリップフロップの記憶の仕組みは、図16の回路が基礎になっているので、Q信号と同時にQ信号も発生するのです。

ところで、図16の回路は双安定なので、確かに1ビットの情報を記憶しますが、好きな情報を記憶できるわけではありません。図16の回路の電源投入時の状態は不定です。2つのNOT回路の入力電圧の閾値のわずかな差や、たまたまその時に発生したノイズなどの微妙な要素で初期状態が決まってっしまいます。

自分(回路の使用者)の好きな情報を記憶しようと思うと、双安定な回路構成にするだけでは不十分で、一方の安定状態から、もう一方の安定状態に遷移させる(移す)仕組みを組み込む必要があります。

この安定状態を遷移させる仕組みの回路構成により、RSフリップフロップ、JKフリップフロップ、Tフリップフロップ、Dフリップフロップなどのバリエーションが発生します。

安定状態を遷移させる仕組みについて説明すると、話が長くなるため、最も簡単な例のみをここで紹介しておきます。

図16の回路に抵抗を2個、押しボタンスイッチを2個付けて作ったのが図20の回路です。

S1とS2の2つのスイッチがOFFの状態では、図20の回路は図16の回路と同じ動作をします。つまり、Q信号がHでQ信号がLの安定状態(Hを記憶した状態)と、Q信号がLでQ信号がHの安定状態(Lを記憶した状態)のいずれかの状態を保持します。

注:S1とS2の2つのスイッチがOFFでも、回路の中にR1とR2の2つの抵抗が残りますが、これらの抵抗には電流が流れないので、電圧降下は発生しません。

スイッチS1のみをONにした場合は、INV1の出力がHかLかにかかわらず、Q信号がLになります。INV1の出力がHの場合は、Q信号の電圧を押し上げる方向にINV1の出力端子が電流を供給するものの、INV1の出力は抵抗R1を介してQ信号につながっており、一方でスイッチS1を介してQ信号がGNDにショートしているので、Q信号はLになります。Q信号がLになると、INV2の働きによりQ信号はHになります。

この様に、スイッチS1のみをONにすると、Q信号がLでQ信号がHになりますが、その後スイッチS1をOFFに戻しても、Q信号がLでQ信号がHの安定状態(Lを記憶した状態)を保持します。つまり、スイッチS1のボタンを押すと、フリップフロップに強制的にLを記憶させる事ができるのです。

この例の様に、外部からの操作で、フリップフロップに強制的にLを記憶させることを、リセットあるいはクリアといいます。

今度は、スイッチS2のみをONにする事を考えます。この場合は、INV2の出力値にかかわらず、Q信号がLになります。Q信号がLになると、INV1の働きにより、Q信号がHになります。つまりHを記憶した状態になります。この状態は、スイッチS2をOFFにしても維持されます。つまり、スイッチS2のボタンを押すと、フリップフロップに強制的にHを記憶させる事ができるのです。

この例の様に、外部からの操作で、フリップフロップに強制的にHを記憶させる事を、セットあるいはプリセットといいます。

S1とS2の2つのスイッチを共にONにした場合は、Q信号とQ信号が共にLになります。この状態は、2つの安定状態のいずれでもないので、S1とS2の2つのスイッチを共にOFFに戻した時に、Q信号がHでQ信号がLの安定状態(Hを記憶した状態)か、Q信号がLでQ信号がHの安定状態(Lを記憶した状態)かのいずれかに戻ります。どちらの安定状態に戻るかは、S1とS2のいずれのスイッチを先にOFFにするかで決まります。ただし、S1とS2を同時にONにした状態は、Q信号とQ信号の真理値が互いに論理反転していないという、例外的な状態になるため、2つのスイッチを同時にONにする操作は禁止するのが一般的です。

以上の様に、図20の回路は、スイッチ操作により、フリップフロップをリセットしたりセットしたりする事ができます。この様なフリップフロップをRSフリップフロップといいます。(RSは、リセット・セットの略) ただし、図20のRSフリップフロップは、Q信号あるいはQ信号を、スイッチでGNDにショートする事により操作する、やや特殊なRSフリップフロップです。外部からHまたはLの真理値を入力する事により動作する、普通のRSフリップフロップの回路構成や動作原理については、この用語集のRSフリップフロップの項を参照してください。

次のページでは、複数のフリップフロップを縦続接続した時の動作や、非同期クリア端子・非同期プリセット端子について説明します。