| 2019年11月27日 | 更新 |

この章では、バイポーラトランジスタを使ったNOT回路の構成法について説明します。

バイポーラトランジスタにはNPNトランジスタとPNPトランジスタの2種類がありますが、この章ではNPNトランジスタを使ったNOT回路の構成法について説明します。NPNトランジスタにかかる電圧や、NPNトランジスタに流れる電流の極性を逆にすれば、PNPトランジスタでもNOT回路を構成する事はできますが、ここでは説明しません。

図37はNPNトランジスタの回路記号です。

NPNトランジスタにはベース、コレクタ、エミッタの3つの端子があります。ベース、コレクタ、エミッタは、それぞれB、C、Eと、アルファベット大文字1文字で省略表記される場合が多いです。

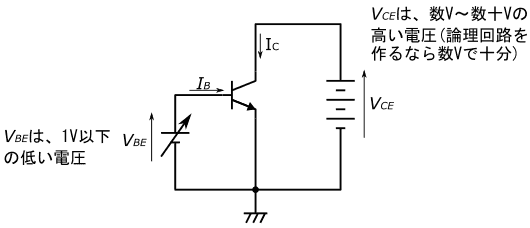

NPNトランジスタは電流増幅作用を持つ半導体素子です。NPNトランジスタに電流増幅させる場合は、図38に示す様に、ベース-エミッタ間に低い電圧VBE(1V以下)を、コレクタ-エミッタ間に高い電圧VCE(数V~数十V程度、論理回路を作る場合は数V)を加えます。

この回路図は、トランジスタの動作原理を説明するための、原理説明図です。この回路図通りの回路で電流増幅の実験などを行うと、VBEが0.6Vを超える付近で、急激にNPNトランジスタに流れる電流(IBやIC)が増え、簡単にトランジスタが発煙・発火します。実際に実験などを行う場合は、VBEを印加するための電源とベースの間に抵抗を挿入するなどして、IBの増加が緩やかになる工夫をします。電源とベースの間に抵抗が挿入されていても、トランジスタのベース-エミッタ間につないだ電圧計の測定値をVBEとすれば、正しい測定結果が出ます。

VCEを一定に保ち、VBEを0Vから徐々に増加させると、ベース電流IBも、VBEの増加につれて増加します。その様子をグラフ化したのが図39です。

図39の特性は、PN接合ダイオードとほぼ同じ特性です。VBEが約0.6Vに達するまではIB≒0とみなせるものの、VBEが約0.6Vを超えると、急激にIBが増加します。

VBEが約0.6Vより低く、IB≒0とみなせる場合は、コレクタ電流ICについてもIC≒0とみなせるのですが、VBEが約0.6Vを超えてくると、IBが流れ始めるのが呼び水になって、ICも流れ始めます。この時に、きっかけになったIBよりも、IBに誘われて流れ始めたICの方が桁違いに大きいのがポイントです。

IBとICの関係を示したのが図40です。

こういう測定をする場合はベース電流をμA単位で表記し、コレクタ電流をmA単位で表記する場合が多く、図40もそれにならっています。そのためグラフを見てもICがIBより桁違いに大きくなっている感じがしませんが、実際にはICの方がはるかに大きな電流です。

図40の様に、ICはIBにおおむね比例して増加し、その比例係数は、エミッタ接地電流増幅率と呼ばれます。エミッタ接地電流増幅率は通常hFEという記号で表わされ、その値はトランジスタによって異なるものの、数十~数百くらいの値になります。

参考:電流増幅回路を設計するならhFEの値が重要になりますが、NOT回路の設計をする場合に、hFEの値はあまり重要ではありません。hFE≫1の条件が成り立っていれば(市販のほとんどのトランジスタはこの条件を満たします)、NOT回路の特性はhFEの値にあまり影響を受けません。

IBが一定の条件でVCEを変化させても、VCEが極端に低い領域を除くと、VCEが変化しても、ICはあまり変化しません。つまり、ICはあまりVCEの影響を受けずに、主にIBにより決まるという事です。

以上が、NPNトランジスタの電流増幅作用に関する説明です。

この様に、電流増幅作用を持つNPNトランジスタを使ってNOT回路を作る場合は、例えば図41に示す回路を使います。この回路は、RTL(Resistor-Transistor Logic)と呼ばれる回路でNOT回路を構成した物になります。

VCCは電源電圧で、普通、数V(例えば5V)に設定します。

ベースに接続された抵抗RBは、入力電圧VINが約0.6Vを超えても、急激にベース電流IBが増えて、NPNトランジスタが過熱しない様に、電流制限の目的で用いられており、ベース保護抵抗と呼ばれます。

コレクタと電源電圧VCCの間の抵抗RCはコレクタ抵抗と呼ばれ、コレクタ電流ICが流れた時に、電圧降下RCICを発生して出力電圧VOUTを下げる働きをします。つまり、出力電圧VOUTは、式(2)により求まります。

RBの値はRCの値との比で決めます。おおむねRBはRCより一桁大きな値にします。例えばRC=1[kΩ]として設計するなら、RB=10[kΩ]などとします。(厳密なものではないので、RB=5[kΩ]でもRB=20[kΩ]でも動作します)

入力電圧VINと出力電圧VOUTの関係をグラフ化したのが図42です。

入力電圧VINが約0.6V以下の領域では、ベース電流IBが流れないので、コレクタ電流ICも流れず、コレクタ抵抗に電圧降下は発生しません。そのため出力電圧VOUTはVCCになります。

ところが、入力電圧VINが約0.6Vを超えると、急にIBやICが流れ始め、VOUTが急降下します。

しかし、VOUTが0Vに近づくと、VOUTの降下が止まります。

VINの上昇に伴い、なぜVOUTが降下するかというと、ICが増加するからでした。(式(2)を参照) もともとなぜICが流れるかというと、トランジスタのコレクタ-エミッタ間に電圧VCEが掛かっているのが原動力になっています。

図41のNOT回路では、コレクタ-エミッタ間電圧VCEは、出力電圧VOUTそのものです。VOUTが0になれば、ICは流れられないのです。

そういう理由で、VOUTがほぼ0になると、IBが増えてもICの増加しなくなり、VOUTはそれ以上降下しなくなります。この現象を飽和といいます。

NPNトランジスタが飽和している時は、IC=hFEIBという関係は成り立たなくなります。(あるいは、飽和が起こるとhFEが低下するという表現もします)

VINが0.6Vより大幅に高くても、VOUTが完全に0Vになるわけではなく、トランジスタの種類やICの大きさにもよりますが、0.1~0.3V程度の電圧は残ります。これをコレクタ飽和電圧と呼びます。

動作の説明が終わったところで、あらためて図42のグラフを見ると、入力電圧が約0.6Vより低ければ、出力電圧はVCCという高い電圧になります。つまりLを入力すればHを出力するのです。

また入力電圧が0.6Vよりも十分高ければ、出力電圧は0.1~0.3Vにまで下がります。つまりHを入力すればLを出力するのです。

この様に、図41の回路はNOT回路として動作します。

ただ図41の回路は、電源電圧に対して閾値(LとHの境目の電圧で図42より0.6Vちょっとだと分かる)があまりにも低いのが、ノイズマージンの確保などの点で問題になる事があります。その場合は抵抗を1本増やして、図43の様な回路を使います。

図43のNOT回路では、入力電圧VINをR1とR2で分圧してからベースに入力するので、閾値をより高く設定できます。

NOT回路を2つ使うと、1ビットの記憶回路を作る事ができます。この記憶回路は、各種フリップフロップやSRAMが情報を記憶する原理になっている回路で、是非とも動作原理を理解しておきたい回路です。

この章では、NOT回路を2つ使った記憶回路の基本的な動作原理について説明します。

図44の様に、2つのNOT回路を環状に接続した回路は、図45および図46に示す様に、2つの安定な状態を取り得ます。

参考:3つのNOT回路を環状に接続した回路は、安定状態を取らずにリング発振器になります。

仮に今、図45の様にU1の入力がLだと仮定すると、U1の出力は逆のHになります。U1の出力はU2の入力に接続されていますから、U2の入力もHになります。そうすると、U2の出力は逆のLになります。U2の出力はU1の入力に接続されていますが、どちらもLなので、矛盾は発生せず、安定状態(時間が経過しても変わらない状態)になります。

次に今、図46の様にU1の入力がHだと仮定します。今度はU1の出力は、入力の逆のLになります。U1の出力はU2の入力に接続されていますから、U2の入力もLになります。そうするとU2の出力は、入力の逆のHになります。U2の出力はU1の入力に接続されていますが、どちらもHなので、矛盾は発生せず、安定状態になります。

この様に、図44の回路には2つの安定状態があるのですが、この回路に電源を投入した時に、どちらの安定状態になるのでしょうか?

実は、どちらの安定状態になるかは、回路の微妙な非対称性(U1とU2の閾値の違いなど)やノイズなどによって決まります。そのため、事前にどちらの安定状態になるかを予測する事は困難です。

このままでは図44の回路に利用価値はなさそうですが、少し手を加えると、2つの安定状態の間を、任意のタイミングで、強制的に遷移させる事ができるようになります。そうなると、2つの安定状態に0と1と(あるいはLとHと)を対応させて、1ビットの情報を記憶する記憶回路として利用する事ができます。

図44の回路に2つの抵抗と、2つのスイッチを追加し、図47の回路にすると、1ビットの記憶回路になります。この回路では、U1の出力電圧を外部に取り出す出力端子も設けました。

SW1とSW2はプッシュスイッチ(押しボタンスイッチ)ですが、通常はOFFになっています。プッシュスイッチについているボタンを押したときにだけ、ONになります。

2つのプッシュスイッチをOFFのまま放置すると、図47の回路は、図48に示すHを出力する安定状態と、図49に示すLを出力する安定状態の、2つの安定状態を取り得ます。

電源投入直後はこれらの安定状態の内、どちらになっているか分かりません。

ここで、図50の様に、SW1のボタンを押してONにしてみます。

SW1がONになると、U2の出力がLであれ、Hであれ、U1の入力を強制的にLにする事ができます。そうすると、U1の出力は、入力の反対のHになります。R1には電流が流れませんので電圧降下は発生せず、U1の出力のHは、そのままU2の入力に伝わります。そうすると、U2の出力は、入力の反対のLになります。

この様にして、スイッチをONにした直後に図50に示した電圧分布に落ち着きます。図50の状態は、SW1がONになっていること以外、図48の安定状態と同じ状態です。この後SW1のボタンを押すのをやめて、OFFにすると、図48の安定状態に移行します。

この様に、SW1をONにしてOFFに戻すと、直前に図48と図49のどちらの安定状態であったかに関わらず、図48の安定状態に移行する事を強制できます。この操作を、出力にHが出る様になる事を考慮して、セットと呼びます。

図47の回路をセットするというのは、出力がHになる安定状態に強制的に移行させるという事ですが、これを2進数の1を記憶させる動作だと解釈する事にします。(正論理の場合は、電圧Hは2進数の1に対応します)

次に、図48と図49のどちらの安定状態か分からない状態で、図51の様に、SW2のスイッチを押してONにしてみます。

SW2がONになると、U1の出力がLであれ、Hであれ、U2の入力を強制的にLにする事ができます。そうすると、U2の出力は、入力の反対のHになります。R2には電流が流れませんので電圧降下は発生せず、U2の出力のHがそのままU1の入力に伝わります。そうすると、U1の出力は、入力の反対のLになります。

この様にして、スイッチをONにした直後に図51に示した電圧分布に落ち着きます。図51の状態は、SW2がONになっていること以外、図49の安定状態と同じ状態です。この後SW2のボタンを押すのをやめて、OFFにすると、図49の安定状態に移行します。

この様に、SW2をONにしてOFFに戻すと、直前に図48と図49のどちらの安定状態であったかに関わらず、図49の安定状態に移行する事を強制できます。この操作を、出力にLが出る様になる事を考慮して、リセットと呼びます。

図47の回路をリセットするというのは、出力がLになる安定状態に強制的に移行させるという事ですが、これを2進数の0を記憶させる動作だと解釈する事にします。(正論理の場合は、電圧Lは2進数の0に対応します)

この様に図47の回路は、SW1のボタンを押すとセット(1を記憶させる事)ができ、SW2のボタンを押すとリセット(0を記憶させる事)ができますが、この回路は、RSフリップフロップと呼ばれる回路の一種です。

参考:RSフリップフロップのRはリセットの頭文字です。またSはセットの頭文字です。またフリップフロップは、1ビット記憶する作用を持つ回路を意味します。フリップフロップには、RSフリップフロップ以外にも、Dフリップフロップ、JKフリップフロップ、Tフリップフロップなど、いくつかの種類がありますが、RSフリップフロップは、それらの中で、最も基本になる物です。

図47のRSフリップフロップを、NPNトランジスタを用いて作ってみましょう。NPNトランジスタでNOT回路を構成する方法は既に説明しているので、その方法を用いて図47の回路内のNOT回路を、NPNトランジスタで構成したNOT回路に置き換えれば、NPNトランジスタを用いてRSフリップフロップを構成する事ができます。

NOT回路をNPNトランジスタで構成するには、図41の回路をそのまま使います。

図44の回路の中のNOT回路を、機械的に図41の回路に置き換えると、図52の回路図が得られます。

Q1、R1、およびR2の部品は、図47の回路のU1に相当するNOT回路を構成しています。またQ2、R5、およびR3の部品は、図47の回路のU2に相当するNOT回路を構成しています。

図52の回路は、このままでRSフリップフロップとして動作しますが、少し改良の余地があります。

Q1とQ2のベースに接続されている抵抗(R1とR6)はどういう働きをしているかというと、Q1やQ2のベースに0.6Vを大きく超える高い電圧が印加された時に、ベース電流が流れすぎてQ1やQ2が過熱してしまうのを防止するための、電流制限用抵抗(ベース保護抵抗)でした。

しかし図52の回路では、R3とR5がQ1のベース電流を制限していますし、R2とR4がQ2のベース電流を制限しています。そのため、R1やR6の抵抗は省略してしまって構わないのです。

図52の回路において、R1とR6を省略し、部品の配置を、回路図が見やすい様に少し変えると、図53の回路図が得られます。

図53の様に、NPNトランジスタなどの増幅素子(あるいはスイッチング素子)を2つ対抗させ、構成したRSフリップフロップを、双安定マルチバイブレータといいます。