今回製作した電子負荷の回路図を再掲しておきます。この電子負荷を設計する際にポイントとなるのが、OPアンプをいかに発振させないかという点です。

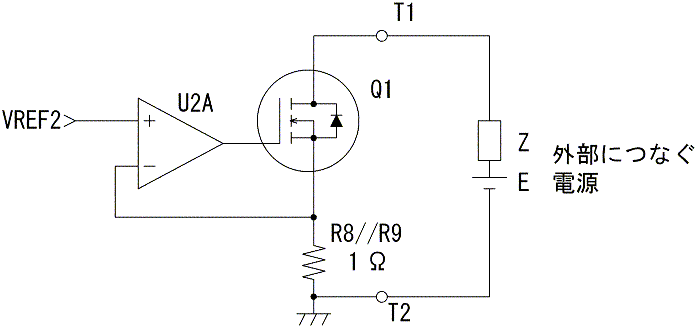

電子負荷が定電流領域で動作している場合の簡略化した等価回路図は次の様になります。

典型的な定電流負荷回路です。U2Aの反転入力端子の電位がVREF2より高ければQ1のゲート電位が上がり、Q1のソース電流が減り、U2Aの反転入力端子の電位が下がるという負帰還が働いており、その結果、1Ωの抵抗の端子間電圧がVREF2の電位と同じになるように制御されます。つまり、T1からT2へ流れる電流は、VREF2の電位でコントロールできるわけです。

Q1はソースフォロワとして動作していますので、T1の電位はU2Aの反転入力端子の電位にはほとんど影響しません。U2Aの出力端子の電位が上がれば反転入力端子の電位も上がりますが、この際の利得は、1倍(0dB)を少し下回ります。

U2AのOPアンプ内部で、ユニティゲイン(利得1倍)動作させても発振しないように位相補償がなされており、ボルテージフォロワの出力段をソースフォロワで電流増幅する形のこの回路も、比較的発振しにくい回路です。

実際の回路では、U2Aの反転入力端子にR10(10kΩ)が入っていますが、これは電子負荷の電源(CN1から供給)が落ちているときにT2がT1より高い電位になった場合、U2Aが壊れるのを防ぐための保護抵抗です。バランスを取るために非反転入力端子側にもR7(10kΩ)を入れています。ただし、U2Aとして、入力バイアス電流がとても小さいOPアンプを使っているので、R7はなくても問題なかったと思います。

R10やR7は、U2Aの寄生容量とCRローパスフィルタを形成します。それにより位相遅れが生じてU2Aの発振が起こらないように、R10やR7に並列に100pFのコンデンサをつなぎ、位相遅れを防いでいます。

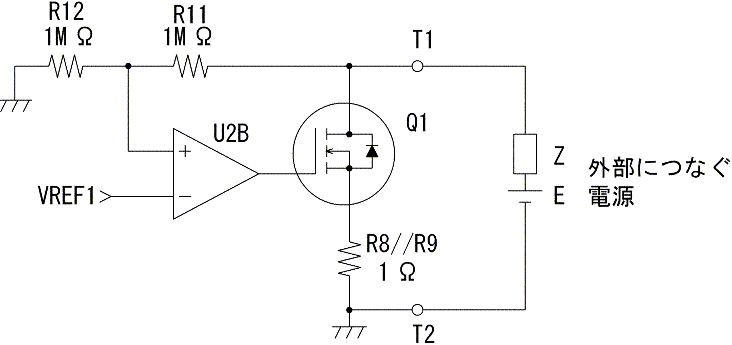

電子負荷が定電圧領域で動作している場合の簡略化した等価回路図は次の様になります。

この回路の場合は、T1の電位の1/2がVREF1より高いとQ1のゲート電圧が上がり、Q1のドレイン電流が増え、外部につないだ電源の内部インピーダンスZで生じる電圧降下が増え、T1の電位が下がるという負帰還が働いています。その結果、T1の電位はVREF1の2倍になるようにコントロールされます。

Q1はソース接地回路として働いており、Zが大きくなるほどソース接地回路の利得も大きくなります。すなわち、どの様な電源が外部につながるかが分からないと、利得が計算できないことになります。また、外部の電源が定電流電源動作をしている場合はZがとても大きくなるため、Q1によるソース接地回路の利得もかなり大きくなることが予想できます。ソース接地回路が利得を持つため、U2A内部の位相補償では補償不足になり、外部にも位相補償回路をつけないと、この回路は容易に発振してしまいます。

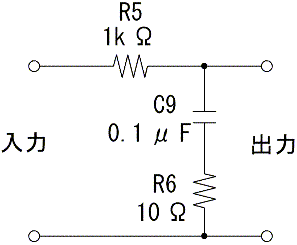

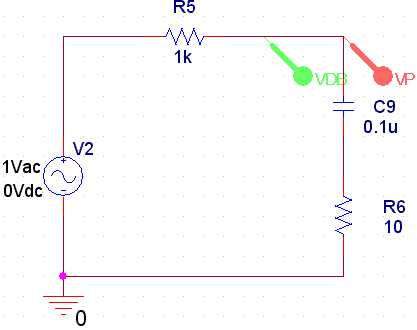

高い周波数での利得を落とし、利得余裕・位相余裕を稼ぐための位相遅れ補償回路を使えば発振を防げます。今回使った位相補償回路を次に示します。この回路は、U2Aの出力端子とQ1のゲートの間に挿入されています。

U2B内部の位相補償がどうなっているのか分からない上に、外部電源のインピーダンスZも特定の値を想定できないため、解析的な方法で位相補償回路の定数を求めることは非常に困難です。そこで、カット&トライで定数を決めました。定電流源を外部につないだ時に利得余裕が最もなくなるため、実験用の電源を定電流動作させ、それをつないでも発振しないように定数を決めます。

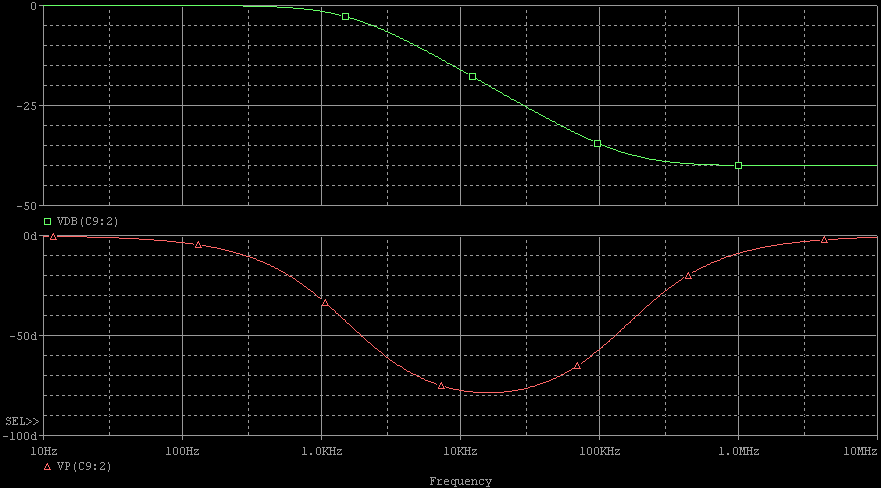

図16の位相遅れ補償回路の周波数特性をPSpiceで解析した結果を図17と図18に示します。

図18は、上が利得[dB]で、下が位相[度]です。利得特性に注目すると、おおよそ1kHz以下では利得は0dBですが、数百kHz以上では-40dBになっています。また位相特性に注目すると、数百Hz~数百kHzの範囲で位相遅れがありますが、高周波・低周波領域では位相の遅れはありません。

高い周波数で利得が約40dB低下しており、また位相遅れもわずかであることから、利得余裕や位相余裕が増し、回路が発振しにくくなります。

あまり過剰な位相補償をすると、例えば外部電源の起電力Eが変動した場合などの過渡応答が悪くなると思われますが、今回製作した電子負荷は、直流の測定に使うのを目的に作ったので、過渡応答は気にしないことにします。また、図16の位相補償回路は、電子負荷が定電流領域で動作している場合にも効き、過補償となって過渡応答が悪くなりますが、やはり気にしないことにします。

図16の位相遅れ補償回路を付けると、外部電源のインピーダンスZが純抵抗の場合はOPアンプが発振しなくなりますが、それでもZが容量性になる場合は、Q1のソース接地回路で位相遅れが発生し、OPアンプが発振してしまいます。これを食い止める確実な方法は、T1の近くにインダクタンス性のインピーダンスを接続し、電源の容量性インピーダンスが直接つながらないようにすることです。そのために、L1の10μHのコイルをつないでいます。コイルだけだと高周波領域でインピーダンスがどんどん上がりますので、並列に1Ωをつないでいます。

L1を使ったお陰で、外部電源に並列に100μFのOSコンデンサをつないでも発振しなくなりました。一方で、図7でお見せしたように、わずかながら定電圧特性が劣化しました。

定電流動作して欲しいときには図14、定電圧動作して欲しいときには図15のような回路として働いて欲しいので、R3、D3、D4からなる回路で、定電圧動作と定電流動作を切り替えています。

2.5Wと比較的小電力用ではありますが、定電圧モードと定電流モードの両方を持った電子負荷を製作しました。小型ですし、省電力ですので、電池駆動でも使えるはずです。(今回はACアダプタをつなげましたが) 一つ作っておくと、色々な測定に使えて便利だと思います。

他にもインターネット上で自作の電子負荷を発表している方はいらっしゃりますが、定電流モードのみで動作するものが多いようです。定電圧モードが必要なかったのかも知れませんが、ひょっとしたら定電圧モードにおける発振対策が大変だったからかもしれません。