| 2018年07月07日 | 更新。 |

アナログ信号を、1(H)か0(L)の2値信号に変調(符号化)する際に、全体の時間の中で1が占める時間の割合でアナログ量を表現する形式の変調方式をPDMあるいはパルス密度変調と呼びます。例えばPWMやPFMは、PDMの一例です。

PDMを利用すれば、電力効率を落とすことなく出力制御ができるため、パワーエレクトロニクスの分野では、電源回路や各種パワーアンプなどに使われます。

また、クロック同期式のPDM変調回路は、一種のA/D変換回路と考えられます。特に後述するΔΣ変調をA/D変換器として用いると、高精度のアナログ部品を多用する事なく、高精度のA/D変換結果が得られます。

PDM信号をLPFにかける付ける事により、簡単にアナログ信号が得られる事から、デジタル方式のPDM変調回路は、D/A変換器としても用いられます。

PDMの手法については色々考えられますが、ここでは、PWMとPFMとΔΣ変調について説明します。

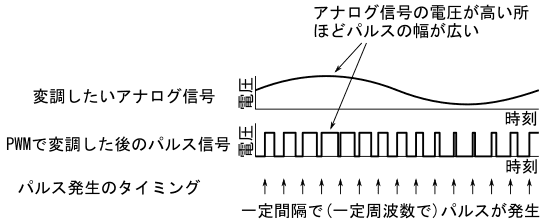

一定の周波数でパルスを発生し、パルスの幅を変える事でアナログ信号をパルス列に変調する手法を、PWM(Pulse Width Modulation)あるいはパルス幅変調と呼びます。

図1にPWM信号の波形を示します。

この図に示す様に、PWMで変調した後のパルス信号は、周波数が一定です。つまり、一定時間ごとに1つのパルスが発生します。

パルスの幅(出力が1になっている部分の時間)は、アナログ信号の電圧が高い所ほど広くなります。この様に、パルスの幅に情報を載せるのがPWMの特長です。

PWMの応用例など、さらに詳しい情報については、PWMの項目をご覧ください。

パルス幅を一定に保ち、周波数を可変にする事で、アナログ信号をパルス列に変調する手法を、PFM(Pluse Frequency Modulation)またはパルス周波数変調と呼びます。

図2にPFM信号の波形を示します。

この図に示す様に、PFMで変調した後のパルス信号は、パルス幅が一定になっています。

一方で周波数(パルスの発生する頻度)は、アナログ信号の電圧が高い所ほど高くなります。この様に、パルスの周波数に情報を載せるのがPFMの特長です。

入力したアナログ信号の電圧が低い時にPFMの周波数が極端に下がる事があるため、入力した信号の周波数とPFMの周波数が近づき、復調時に両者をLPFで十分に分離できなくなる事があります。この様な欠点があるものの、スイッチング電源に応用すれば、低負荷時にスイッチング周波数を下げる事ができ、電力効率が上昇するため、電源回路の設計に用いられる事が多くあります。

ΔΣ変調(デルタ・シグマ変調)はΔΣ変調回路によりPDM信号を得る手法です。ΔΣ変調は、ΣΔ変調と呼ぶ事もあります。

ΔΣ変調回路には各種のバリエーションがありますが、ここでは、動作の理解がしやすい図3の回路で説明をします。

このΔΣ変調回路は、減算回路と、積分回路と、ヒステリシスコンパレータの3種類の回路から構成されています。

減算回路は、変調したいアナログ信号の電圧から、ヒステリシスコンパレータの出力電圧を引き、積分回路に出力します。

積分回路は、減算回路から受け取った電圧を時間積分し、ヒステリシスコンパレータに出力します。

ヒステリシスコンパレータは、減算回路の入力電圧を2値化します。このヒステリシスコンパレータの入出力電圧特性を図4に示します。

このヒステリシスコンパレータは、入力電圧がVT以上なら、出力電圧はVMになります。また、入力電圧が−VT以下なら、出力電圧が−VMになります。そして、入力電圧が−VT~VTの範囲内なら、出力電圧が、直前の出力電圧に依存します。

最初に入力電圧が−VT以下である場合、入力電圧を徐々に上げていくと、入力電圧がVTに達するまでは、出力電圧が−VMのままです。そして、入力電圧がVTを超えた瞬間に、出力電圧がVMに変わります。

最初に入力電圧がVT以上である場合は、入力電圧を徐々に下げていくと、入力電圧が−VTに達するまでは、出力電圧がVMのままです。そして、入力電圧が−VTを下回った瞬間に、出力電圧が−VMに変わります。

ヒステリシスコンパレータの出力電圧を減算回路に戻すと、負帰還がかかります。帰還ループ内にヒステリシスコンパレータが含まれているため、この回路は安定する事ができず、自励発振をします。

図3の回路の各部の波形を図5に示します。

この図を見ると分かる様に、変調したいアナログ信号の電圧が高いほど、PDM出力のパルス密度(出力電圧が正になる時間の割合)が高くなり、きちんとPDM変調が行われている事が分かります。

この回路は、PDM出力が変調したいアナログ信号を近似した際の誤差(減算回路の出力)の時間積分(積分回路の出力)がほぼ0になる様に(厳密にいうと−VT~VTの範囲内に収まる様に)負帰還がかかります。そのため短期的な(PDM信号の周波数程度の高周波数の)誤差は発生しますが、長期的な(変調したいアナログ信号程度の低周波数の)誤差がほぼ発生しない様に動作します。

ただし、変調したいアナログ信号電圧が上限のVMまたは下限の−VMに近いと、PDM出力の周波数が極端に落ち、低い周波数の誤差(ノイズ)が発生します。そのため、高精度なPDMを行いたい場合は、回路に入力する信号の振幅を低めに抑える工夫をする場合があります。

ΔΣ変調に関するさらに詳しい説明については、ΔΣ変調の項目をご覧ください。