| 2020年01月31日 | 更新 |

ΔΣ変調(デルタ・シグマ変調)は、信号の差を取る減算回路、信号の時間積分を行う積分回路、および、出力値を入力に帰還して出力値が目標値に近づく様に制御を行うための負帰還回路などから構成されるΔΣ変調回路により、PDM変調やA/D変換やD/A変換を行う手法の事です。ΔΣ変調は、ΣΔ変調と呼ぶ事もあります。

ΔΣ変調回路の主な用途としては、電力効率の良いパワーアンプであるD級アンプや、1ビットのA/D変換器、マルチビットのPCM信号をPDM信号に変換するPDM変調器(これにLPFを付けるとD/A変換器になる)などが挙げられます。

A/D変換のためにΔΣ変調を使う場合、扱う信号の帯域が狭いと、高倍率のオーバーサンプリングを行う事で非常にS/N比の高いA/D変換器が構成きます。この様なA/D変換器は、例えば心電図や脳波測定のための高S/N比、高ダイナミックレンジのA/D変換器として利用されています。

またオーディオの世界では、DSDと呼ばれる、PDMを用いた記録フォーマットが使われていますが、アナログ信号をDSDフォーマットとして記録するのにも、ΔΣ変調を応用した1ビットA/D変換器が使われます。

なお、ΔΣ変調のΔは減算回路で出力電圧の誤差を計算する事に由来しており、ΔΣ変調のΣは、その誤差を時間積分する事に由来しています。

以下に、ΔΣ変調をPDM変調に使う場合と、A/D変換に使う場合について説明します。

ΔΣ変調をPDM変調(パルス密度変調)に用いる場合について説明します。

参考:PDM変調の意味については、この用語集のPDMの項目をご覧ください。

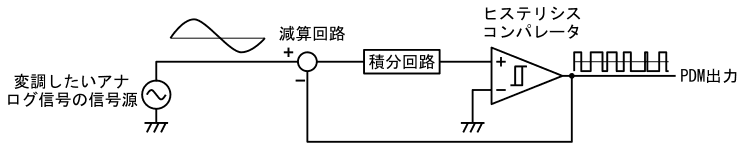

PDM変調に用いられるΔΣ変調回路には各種のバリエーションがありますが、ここでは、動作の理解がしやすい図1の回路で説明をします。

このΔΣ変調回路は、減算回路と、積分回路と、ヒステリシスコンパレータ(シュミットトリガ回路の一種)の3種類の回路から構成されており、ヒステリシスコンパレータの出力が減算回路に負帰還されています。

このΔΣ変調回路では、入力したアナログ信号を、PDM信号に変換できます。(図2参照)

減算回路は、変調したいアナログ信号の電圧から、ヒステリシスコンパレータの出力電圧を引き、積分回路に出力します。

積分回路は、減算回路から受け取った電圧を時間積分し、ヒステリシスコンパレータに出力します。

ヒステリシスコンパレータは、減算回路の入力電圧を2値化します。このヒステリシスコンパレータの入出力電圧特性を図3に示します。

このヒステリシスコンパレータは、入力電圧がVT以上なら、出力電圧はVMになります。また、入力電圧が−VT以下なら、出力電圧が−VMになります。そして、入力電圧が−VT~VTの範囲内なら、出力電圧が、直前の出力電圧に依存します。

最初に入力電圧が−VT以下である場合、入力電圧を徐々に上げていくと、入力電圧がVTに達するまでは、出力電圧が−VMのままです。そして、入力電圧がVTを超えた瞬間に、出力電圧がVMに変わります。

最初に入力電圧がVT以上である場合は、入力電圧を徐々に下げていくと、入力電圧が−VTに達するまでは、出力電圧がVMのままです。そして、入力電圧が−VTを下回った瞬間に、出力電圧が−VMに変わります。

ヒステリシスコンパレータの出力電圧を減算回路に戻すと、負帰還がかかります。帰還ループ内にヒステリシスコンパレータが含まれているため、この回路は安定する事ができず、自励発振をします。

図1の回路の各部の波形を図4に示します。

この図を見ると分かる様に、変調したいアナログ信号の電圧が高いほど、PDM出力のパルス密度(出力電圧が正になる時間の割合)が高くなり、きちんとPDM変調が行われている事が分かります。

この回路は、PDM出力が変調したいアナログ信号を近似した際の誤差(減算回路の出力)の時間積分(積分回路の出力)がほぼ0になる様に(厳密にいうと−VT~VTの範囲内に収まる様に)負帰還がかかります。そのため短期的な(PDM信号の周波数程度の高周波数の)誤差は発生しますが、長期的な(変調したいアナログ信号程度の低周波数の)誤差がほぼ発生しない様に動作します。

ただし、変調したいアナログ信号電圧が上限のVMまたは下限の−VMに近いと、PDM出力の周波数が極端に落ち、低い周波数の誤差(ノイズ)が発生します。そのため、高精度なPDMを行いたい場合は、回路に入力する信号の振幅を低めに抑える工夫をする場合があります。

ここでは、図1の回路の「変調したいアナログ信号」が、直流電圧VSであると仮定して、より詳細な回路動作の説明を行います。

図1の「変調したいアナログ信号」(入力信号)が電圧VSの直流電圧源だった場合の回路図を図5に示します。

ただし、入力電圧VSは、式(1)の関係を満たすとします。(この関係を満たさないと、出力が飽和し、うまくPDM変調できません)

減算回路は、+の記号の端子に加えられた電圧から、−の記号の端子に加えられた電圧を引き、その引き算の結果に相当する電圧を出力します。

+の記号の端子に加えられた電圧はVSで、−の記号の端子に加えられた電圧は、このΔΣ回路の出力電圧vout(t)(ただし、tは時刻を表す変数)ですから、減算回路の出力電圧v1(t)は式(2)で与えられます。

積分回路は入力電圧を時間積分し、その積分結果に正の係数Kを掛けた電圧を出力します。よって、積分回路の出力電圧v2(t)は、式(3)で与えられます。

ヒステリシスコンパレータの出力電圧、すなわちPDM変調回路の出力電圧vout(t)は、ヒステリシスコンパレータの入力電圧v2(t)の値によって、図3に示した様に−VMまたはVMの電圧を取ります。

今、vout(t)=VMの場合は、式(3)にvout(t)=VMを代入する事により、式(4)が得られます。

ここで、式(1)の関係式より、VM−VSが正の値を取る事に注意してください。

式(4)よりddtv2(t)が負の定数−K(VM−VS)になるので、コンパレータが電圧VMを出力している時は、v2(t)が右肩下がりの一次関数になる事が分かります。

今度はvout(t)=−VMの場合について考えます。この場合、式(3)にvout(t)=−VMを代入する事により、式(5)が得られます。

式(5)よりddtv2(t)が正の定数K(VM+VS)になるので、コンパレータが電圧−VMを出力している時は、v2(t)が右肩上がりの一次関数になる事が分かります。

時刻t=0において、v2(0)=0で、vout(0)=VMだったと仮定します。そうすると、v2(t)が−VTに達するまでは、v2(t)が傾き−K(VM−VS)の、右肩下がりの一次関数になります。これは、図6に示したグラフの期間Aに相当します。

v2(t)が−VTに達すると、vout(t)が−VMに変化します。この時、v2(t)の傾きはK(VM+VS)に変化し、右肩上がりの一次関数になります。この状態がv2(t)がVTに達するまで続きます。これは、図6の期間Bに相当します。

v2(t)が上昇し続ける時間(期間Bの継続時間)TRは、v2(t)の変化幅2VTを、傾きK(VM+VS)で割る事で、式(6)の様に求まります。

v2(t)がVTに達すると、再びvout(t)がVMに変化します。これに伴い、v2(t)は傾き−K(VM−VS)で減少し始め、この減少はv2(t)が−VTに達するまで続きます。これは、図6の期間Cに相当します。

v2(t)が減少し続ける時間(期間Cの継続時間)TFは、v2(t)の変化幅−2VTを、傾き−K(VM−VS)で割る事で、式(7)の様に求まります。

出力電圧vout(t)の時間平均値Vaveは式(8)の様に求まります。

式(8)の導出過程を見ていると、出力電圧の時間平均値Vaveが入力電圧VSと一致するのは、すごい偶然の様な気がしてきます。

しかし図5の回路は、出力電圧vout(t)と入力電圧VSの差を減算回路で求め、その出力を積分回路で時間積分し、その結果が一定範囲内に入る様に制御しています。つまり、言い方を変えると、VaveがVSと一致する様に制御しているのです。

vout(t)の発振周波数fも求めておきましょう。fは式(9)で求まります。

式(9)よりVSとfの関係をグラフ化すると、図7の様になります。

この様に、上に凸の放物線のグラフになり、VS=0の時に最大周波数K4VTを取ります。またVSがVMや−VMに近づくと、発振周波数が限りなく0に近づきます。

前節で説明したとおり、直流信号VSを入力した時のPDM変調回路の出力の方形波電圧波形の時間平均値Vaveは、入力電圧VSに一致します。

よって図1の様に、入力にPDM変調信号の発振周波数fよりも十分に低い周波数の交流信号を入力しておき、さらにPDM出力の後段に、図8に示す様なLC型2次フィルタなどのLPFを接続して、PDMの発振周波数f以上の成分は十分に低減し、入力信号の周波数の成分は十分に通過する様にしておけば、負荷抵抗RLには入力信号が再生されます。

図8の回路において、減算回路の+側端子の入力インピーダンスが、負荷インピーダンスRLよりも十分に大きければ、この回路はパワーアンプ(電力増幅器)として機能します。さらに、LPFとしてLC型の、パッシブで電力損失のない回路構成の物を使い、ヒステリシスコンパレータの出力段を、−VMとVMの電源電圧をMOS-FETなどの電力損失の少ないスイッチで切り替える構成にすれば、非常に電力効率が良いパワーアンプになります。

この様に低損失のスイッチ素子と、LC型の無損失なLPFを組み合わせて作った、高効率のパワーアンプを、D級パワーアンプ(または単にD級アンプ)と呼びます。

図7に示した様に、入力信号電圧がVMや−VMに近くなると、PDM変調回路の発振周波数が下がってきて、LPFでその発振周波数成分を取り除く事が難しくなるので、VMは入力信号の最大振幅よりもある程度(数十%くらい)大きく設定して、発振周波数が極端に下がらない様にする方が、信号品質が確保しやすくなります。

次のページでは、ΔΣ変調をA/D変換に用いる場合について説明します。