| 2019年07月29日 | 更新。 |

フリップフロップを何個か用意し、それらのフリップフロップの個数と同じビット数の2進数の数値を記憶できるようにした回路をレジスタ(register)といいます。

狭義のレジスタは、単に数値を記憶させ、その数値を読み出せるようにした回路ですが、広義のレジスタは、シフトレジスタやカウンタの様に、記憶した数を元に何かの演算をし、合図(クロック)が入るごとに演算結果に従って記憶内容を更新する機能を持った回路も含みます。

狭義の演算機能を持たない、単に数値の記憶と読み出しの機能だけのレジスタを、広義のレジスタと区別する際に、ストレージレジスタ(storage register)という用語を使う場合があります。

なお、抵抗器を英訳するとresistorとなります。このページで解説するregisterも、抵抗器を表すresistorも、カタカナ表記するとレジスタになるので、注意が必要です。抵抗器については、抵抗の項目をご覧ください。

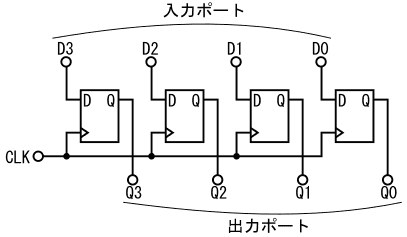

ストレージレジスタは、例えばDフリップフロップをレジスタのビット数と同じ数だけ使うと作れます。図1は、4つのDフリップフロップを使って4ビットのストレージレジスタを構成した例です。

この図において、D0~D3の4つの端子が入力ポートで、これらの端子に、ストレージレジスタに記憶させたい4ビットの数値を入力します。

またCLK信号は、数値をストレージレジスタに書き込むタイミングを知らせる信号です。CLK信号が立ち上がるタイミングで、ストレージレジスタは入力ポートの数値を記憶します。

Q0~Q3の4つの端子が出力ポートで、これらの端子に、記憶している数値が常時出力されています。

一方で、広義のレジスタは、情報を記憶するフリップフロップの周辺に、簡単な演算回路を備えています。図2は、4つのDフリップフロップと、4つのマルチプレクサと、演算回路を用いて、4ビットの広義のレジスタを構成した例です。

図2の回路図に出てくる図3の回路記号は、2入力のマルチプレクサを表しています。マルチプレクサは、複数(この場合2つ)の入力信号の内1つを選択して出力する論理回路です。

Y信号は2つの入力信号(A信号とB信号)のどちらかを出力する出力端子です。

S信号は、Y信号に出力する信号を選択するための信号です。S信号がHなら、Y信号にA信号が出力されます。S信号がLなら、Y信号にA信号が出力されます。

図2の中に描いてある演算回路は、4つの入力信号I0~I3を元に何らかの演算を行い、演算結果を4つの出力信号R0~R3に出力する回路です。この演算回路の種類により、レジスタの種類が変わります。

図2の回路において、LD信号がHの場合は、4つのマルチプレクサがD0~D3の信号を出力しますから、演算回路の出力信号(R0~R3)は無視されます。この時、図2は図1のストレージレジスタと等価になります。

よって、図1のストレージレジスタは、図2の広義のレジスタにおいて、LD信号がHに固定された、特殊な例と解釈する事ができます。

一方で、LD信号がLになりうる広義のレジスタにおいては、LD信号がHの状態でCLK信号が立ち上がると、レジスタの初期値を読み込みます。

LD信号がLの場合は、4つのマルチプレクサが、演算回路の出力信号(R0~R3)を出力しますから、この時図2は図4の様に書き換えられます。

図4の回路では、CLK信号が立ち上がるたびに、直前の出力信号(Q0~Q3)を演算回路に通した値(R0~R3)に、レジスタの記憶内容が更新されます。

広義のレジスタの例として、シフトレジスタを取り上げます。

図2の回路の中の演算回路が、図5の様に入力を1ビット右シフトする回路であれば、図2の回路はパラレル入力機能付きのシフトレジスタとなります。

注:ここではI3とR3をMSB、I0とR0をLSBと考えています。

図2の回路図に出てくる演算装置が図5であるとすると、図2は図6の様に書き換えられます。

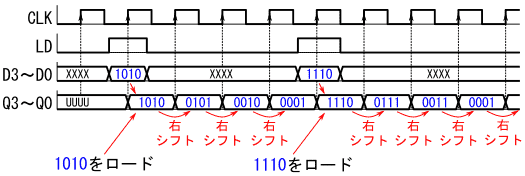

図6の回路のタイミングチャートの例を図7に示します。

D3~D0がXXXXになっている部分は、D0、D1、D2およびD3の4つの入力が、0(L)であっても1(H)であっても、回路の動作には関係ない事(Don't care)を示しています。Q3~Q0がUUUUになっている部分は、Q0、Q1、Q2、Q3の4つの入力が、不定(0であるか1であるかが分からない)である事を示しています。

このタイミングチャートに示した様に、図6の回路は、LD信号がLの場合には、CLK信号の立ち上がりのタイミングでQ3~Q0の信号を右シフトします。

また、LD信号がHの場合には、CLK信号の立ち上がりのタイミングでD3~D0の信号をレジスタ(4つのDフリップフロップ)に書き込み、Q3~Q0信号に出力します。

図6の回路図において、LD信号がLの場合の等価回路は図8の様になります。この状態なら、シフトレジスタである事が分かり易いでしょう。

図6のシフトレジスタにおいて、D3~D0に何かの値をセットし、LD信号をHにした状態で、CLK信号を立ち上げ、次に、LD信号をLにしてから、CLK信号を3回立ち上げると、CLK信号の立ち上がりに同期して、最初にD3~D0にセットした値を、LSBから順に1ビットずつ、シリアル信号としてQ0端子に出力する事ができます。つまり、パラレル-シリアル変換回路として使う事ができます。

シフトレジスタのさらに詳しい話は、この用語集のシフトレジスタの項目をご覧ください。

広義のレジスタの別の例として、アップカウンタを取り上げます。

図2の回路の中の演算回路が、図9に示す様な、入力に1を足す回路であれば、図2の回路は初期値設定機能付きのアップカウンタとなります。(さらにD3~D0のすべてをGNDにつなげば、リセット機能付きのアップカウンタになります)

参考までに、図9の回路の真理値表を表1に示します。

| 入力信号 | 出力信号 | 備考 | ||||||

|---|---|---|---|---|---|---|---|---|

| I3 | I2 | I1 | I0 | R3 | R2 | R1 | R0 | |

| L | L | L | L | L | L | L | H | 0000+1=0001 |

| L | L | L | H | L | L | H | L | 0001+1=0010 |

| L | L | H | L | L | L | H | H | 0010+1=0011 |

| L | L | H | H | L | H | L | L | 0011+1=0100 |

| L | H | L | L | L | H | L | H | 0100+1=0101 |

| L | H | L | H | L | H | H | L | 0101+1=0110 |

| L | H | H | L | L | H | H | H | 0110+1=0111 |

| L | H | H | H | H | L | L | L | 0111+1=1000 |

| H | L | L | L | H | L | L | H | 1000+1=1001 |

| H | L | L | H | H | L | H | L | 1001+1=1010 |

| H | L | H | L | H | L | H | H | 1010+1=1011 |

| H | L | H | H | H | H | L | L | 1011+1=1100 |

| H | H | L | L | H | H | L | H | 1100+1=1101 |

| H | H | L | H | H | H | H | L | 1101+1=1110 |

| H | H | H | L | H | H | H | H | 1110+1=1111 |

| H | H | H | H | L | L | L | L | 1111+1=0000 |

図2の回路に、図9の回路を当てはめて作ったアップカウンタは、LD信号がHの状態でCLK信号を立ち上げると、D3~D0の値をレジスタに書き込みます。またLD信号がLの状態でCLK信号を立ち上げると、レジスタの値が1増えます。(ただしレジスタの値が1111の場合は、繰り上がりを無視して、次は0000になります)

注意:1111や0000の様に緑色で表示した数値は、2進数で表記されている事を示しています。

この回路のタイミングチャートの例を図10に示します。