| 2022年04月23日 | 更新。 |

74HC164は、74HCシリーズの高速CMOSロジックICの一つで、シリアル入力、パラレル出力の8ビットのシフトレジスタの機能を持っています。

シリアル入力端子を2つ持ち、それら2つの入力の両方がHになった時にHが、一方でもLになるLとが、最初のDフリップフロップに読み込まれます。

また、全Dフリップフロップ共通の負論理の非同期リセット端子も備えています。

74HC164は、シリアル入力端子にシリアル信号を入力すると、パラレル出力端子から信号をパラレル形式で出力する、シリアル-パラレル変換回路として通常は使われます。

74HC164よりも入力電圧の閾値を下げてTTLと接続できるようにした74HCT164や、74HC164の高速版の74AC164、74HCT164の高速版の74ACT164、TTLの74LS164も、機能やピン配置は、このページで説明する74HC164と同じです。

74HC164の入手先を知りたい方は、このページの最後の購入ページの一覧表をご利用ください。

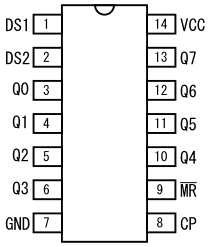

74HC164のピン配置を図1に示します。

注:このページは、Texas Instruments社のCD74HC164のデータシートを参考に記述していますので、ピンの名称はそのデータシートに従っています。他社の互換ICの場合、ピン名称が異なる場合がある事に注意してください。

各端子の意味を、表1にまとめました。

| 名称 | 意味 |

|---|---|

| DS1~DS2 | シリアル信号の入力端子です。パラレル化したいシリアル信号をクロック(CP信号)に同期して入力します。シフトレジスタに信号が入力される前に、DS1とDS2の論理積(AND)が取られます。つまり、DS1とDS2の両方の端子にHが入力されたときのみ、シフトレジスタのシリアル入力端子にHが入力され、DS1とDS2の少なくとも一方がLの場合は、シフトレジスタのシリアル入力端子にLが入力されます。 |

| Q0~Q7 | パラレル信号の出力端子です。MR信号がHの状態でクロック(CP信号)が立ち上がると、Q0~Q6の信号がそれぞれQ1~Q7の信号にシフトします。Q0信号には、DS1信号とDS2信号の論理積(AND)が取り込まれます。 |

| CP | クロック信号の入力端子です。MR信号がHの時に、CP信号の立ち上がりに同期してシフトレジスタがシフト動作します。 |

| MR | 負論理の非同期リセット信号の入力端子です。MR信号がLになると、シフトレジスタを構成する全てのDフリップフロップがリセットされ、出力(Q0~Q7信号)がLになります。 |

| VCC | 電源端子です。74HC164、および74AC164の場合は、この端子に2~6Vの範囲の電源を供給します。74HCT164、74ACT164および74LS164の場合は、この端子に5Vの電源を供給します。 |

| GND | グランド端子です。 |

詳しい説明は、この用語集のシフトレジスタのページをご覧ください。ここでは概略だけを説明します。

74HC164の真理値表を表2に示します。

| 入力信号 | 出力信号 | 動作 | ||||

|---|---|---|---|---|---|---|

| MR | CP | DS1 | DS2 | Q0 | Q1~Q7 | |

| L | X | X | X | L | 全てL | リセット |

| H | L | X | X | q0 | q1~q7 | 保持 |

| H | H | X | X | q0 | q1~q7 | |

| H | ↓ | X | X | q0 | q1~q7 | |

| H | ↑ | L | L | L | q0~q6 | シフト(Q0はL) |

| H | ↑ | L | H | L | q0~q6 | |

| H | ↑ | H | L | L | q0~q6 | |

| H | ↑ | H | H | H | q0~q6 | シフト(Q0はH) |

ただし、表2には次の記号が使われています。

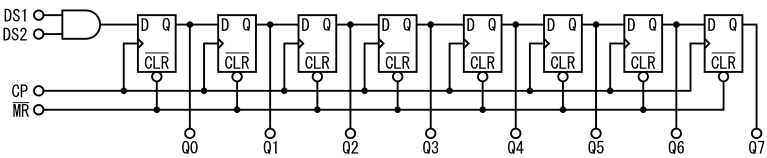

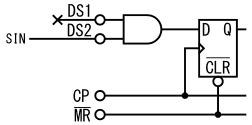

表2の真理値表を満たす様に74HC164の等価回路を考えると、図2の様になります。

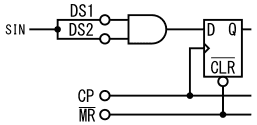

ここで図3の様な回路記号が出てきますが、これは負論理の非同期クリア端子(CLR)を持ったDフリップフロップです。

非同期クリア端子を持ったDフリップフロップは、CLR信号がHの場合は、通常のDフリップフロップと同様に、クロック(CLK信号)の立ち上がりでD信号を取り込み、Q信号に出力する動作をします。

一方でCLR信号がLになると、D信号やCLK信号やDフリップフロップが記憶していた真理値(CLR信号がLになる直前のQ信号の値)にかかわらず、Dフリップフロップの記憶する値が強制的にLにされ、CLR信号がHになった後にクロックの立ち上がりでD信号からHが取り込まれるまで、Q信号はLのままになります。この動作を非同期クリアまたは非同期リセットといいます。

図4に、非同期クリア端子を持ったDフリップフロップのタイミングチャートの例を示します。

3つの入力端子(CLK、CLR、D)の中ではCLR端子の信号が最優先で処理されます。そのため、CLRをLにすれば、クロック(CLK信号)が供給されていない時にでもDフリップフロップにの値をクリア(リセット)する事ができます。

電源投入時には、(Dフリップフロップを含む)フリップフロップの初期状態は不定(LになるのかHになるのか予測できない状態)です。初期状態が不定のまま同期回路(フリップフロップを含む回路)を動作させると、予期しない動作をすることがありますので、通常は電源投入直後にリセット信号でフリップフロップの状態を強制的にL(場合によってはH)に確定してしまいます。

電源投入直後にリセットをかける場合は、その時点でクロック信号が供給されている保証がありません。というのは、電源投入後にクロック発振器がクロック信号を供給し始めるまでには、意外と長い時間がかかるからです。例えば、水晶発振回路でクロックを発生する場合は、クロックが安定して供給されるまでmsオーダーの長い時間がかかります。

この点では、非同期クリア端子を持ったDフリップフロップの場合、クロックがなくても値をクリアできるため、電源投入直後のリセットが確実にかかります。

参考:同期クリア端子を持ったフリップフロップの場合、クロック信号が供給されていないとリセットがかかりません。そのため、フリップフロップの初期化には、クロック信号が確実に安定供給されるようになるまで、リセットをかけ続ける必要があります。

非同期クリア端子を持ったDフリップフロップの動作を踏まえて、図2の74HC164の等価回路のタイミングチャート(つまり74HC164そのもののタイミングチャートともいえる)の例を図示すると、図5の様になります。

タイミングチャートの左端で、MR信号がLになっている期間がありますが、MR信号がLになったタイミングで、8つのDフリップフロップがリセットされ、Q0~Q7の値がLに確定します。これが電源投入直後のリセットです。

その後8波のクロックがCP端子に入力されますが、クロックの立ち上がりのタイミングで、DS2端子に入力されたシリアルデータをシフトレジスタに取り込みます。8波目のクロックの立ち上がりのタイミングで、Q0~Q7の端子に、データがパラレルに出力されます。

その後、しばらく時間をおいて、もう8波のクロック(9~16波目)がCP端子に入力されます。この時にも先ほどと同様、クロックの立ち上がりのタイミングでDS2端子に入力されたシリアルデータをシフトレジスタに取り込むのですが、9波目~12波目までのクロックの立ち上がりのタイミングでは、DS1端子にLが入力されています。DS1信号とDS2信号は論理積(AND)を取った後にシフトレジスタのシリアル入力端子に入力されるので、この期間(DS1信号がLの期間)内では、DS2信号がマスクされて、シフトレジスタに入力する信号が強制的にLになります。

16波目のクロックが立ち上がった瞬間にQ0~Q7の端子にデータがパラレルに出力されるのですが、Q0~Q3の4ビットの信号はDS2端子から入力された信号を反映しているのに対し、Q4~Q7の端子はDS1信号によりマスクされた影響で、値がすべてLになっています。

74HC164の機能を部分的に使わず、使用しない端子が生じる事があります。出力端子(Q0~Q7)の場合は、使わない端子を単にオープンにする(どこにも接続しない)だけでいいのですが、未使用の入力端子は適切に処理する必要があります。この節では、未使用の入力端子の処理法について説明します。

74HC164は、DS1とDS2の2つのシリアル入力端子があり、それらの端子に入力された信号の論理積(AND)を取ってからシフトレジスタに入力する回路構成になっています。この事により、図5に示した様に、DS1信号とDS2信号の内の一方をマスク信号として使う事により、シリアルデータの特定のビットをマスクして強制的にLにする様な使い方ができます。

しかし、シリアル入力端子が1つでいい使用例も多くあります。その場合は、図6の様にDS1端子とDS2端子の内の一方にHを入力するか、図7の様にDS1端子とDS2端子に同じ信号を入力する事で対応できます。

参考:TTLデバイスの74LS164の場合、オープンになった入力端子はHが入力されたものとして処理されるため、図8の様にDS1とDS2の内の一方をオープンにしておくという対処法も考えられます。しかし、ノイズ耐性や、後にCMOSデバイスに置き換える事を考えると、お勧めできる方法ではありません。CMOSデバイスである74HC164、74HCT164、74AC164および74ACT164では、未使用の入力ピンをオープンのまま放置しないでください。消費電流が増えたり、動作が不安定になったり、最悪の場合デバイスがラッチアップして壊れる可能性があります。

非同期リセットを行わない場合は、図9の様にMR端子にHを入力してください。

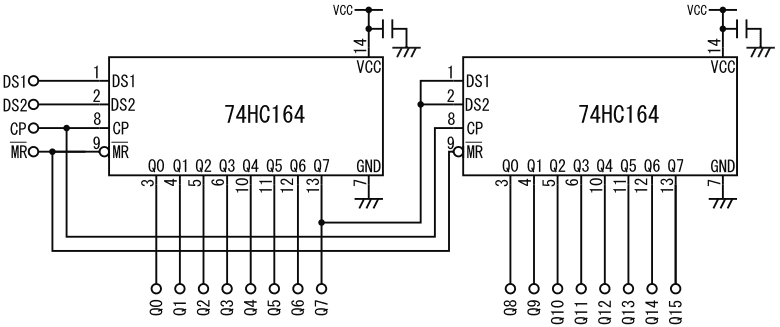

用途によっては、シフトレジスタのビット数が8ビットでは不足する場合があります。図10の様に2つの74LS164を接続すれば、16ビットのシフトレジスタとして使用できます。また、同様の方法で3つ以上の74LS164を接続する事により、24ビット以上のシフトレジスタとして使用する事ができます。

参考:8ビット未満のシフトレジスタでいい場合は、使わない出力端子をオープンにします。例えば5ビットのシフトレジスタが必要な場合は、Q0~Q4の出力端子だけを使い、Q5~Q7の出力端子はオープンにします。同様に、図10の回路でQ0~Q9の出力端子のみを使い、Q10~Q15の出力端子をオープンにすれば、10ビットのシフトレジスタになります。

趣味の電子工作で74HC164、および同機能のIC(74AC164等)を使う方を想定して、インターネット上で購入できるサイトへのリンクを集めました。下の表で部品の型番をクリックすると、販売ページにジャンプします。

なお、この表は2018年12月時点での情報をまとめたものです。

ユニバーサル基板で試作する場合は、DIPパッケージの製品を購入してください。

| 企業名・店舗名 | 部品の型番 | パッケージ | メーカー | 備考 |

|---|---|---|---|---|

| 秋月電子 | SN74HC164N | DIP | TEXAS INSTRUMENTS | |

| SN74HC164DR | SOIC | TEXAS INSTRUMENTS | 4個セット | |

| CD74AC164E | DIP | TEXAS INSTRUMENTS | ||

| マルツ | SN74HC164N | DIP | TEXAS INSTRUMENTS | |

| TC74HC164AF(F) | SOP | 東芝 | 在庫限り。 | |

| TC74VHC164F | SOP | 東芝 | 74VHCシリーズ。 | |

| 共立エレショップ | 74HC164 | DIP | 各社 | どのメーカーの製品が届くか分からないので、微妙な特性が問題になる場合は要注意。 |

| 74LS164 | DIP | 各社 | この製品はCMOSではなくTTLです。どのメーカーの製品が届くか分からないので、微妙な特性が問題になる場合は要注意。 | |

| 千石電商 | TC74HC164AP | DIP | 東芝 | 在庫限り。 |

| SN74LS164N | DIP | TEXAS INSTRUMENTS | この製品はCMOSではなくTTLです。 | |

| RSコンポーネンツ | 74HC164D | SOIC | Nexperia |