| 2024年02月28日 | 更新 |

メカニカルリレーを含む機械的なスイッチでは、バウンスやチャタリングと呼ばれる、意図しない接点の開閉が生じます。

バウンス(bounce)とは、スイッチの接点が閉じてON状態になる時、あるいはスイッチの接点が開いてOFF状態になる時に、単純にOFF→ONやON→OFFにならずに、OFF→ON→OFF→ONとか、ON→OFF→ON→OFF等の、ONとOFFを繰り返す不安定な現象が一時的に起こる事を指す用語です。

参考:水銀スイッチや水銀リレーではスイッチの接点が水銀で濡れた状態になっています。バウンスの対策が、その水銀の粘性と導電性を用いる事により行われており、機械的なスイッチなのに(半導体スイッチではないのに)バウンスが発生しません。ただ有害物質の水銀を部品に使うのは難しいため、今では水銀スイッチや水銀リレーの入手は困難になりました。

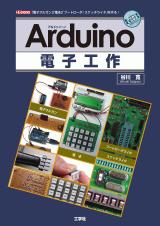

例えば押しボタンスイッチを押して、スイッチをONする事を考えてみてください。ボタンを押す事によりボタン側の電極は押し出されて固定電極に触れます。しかし、電極間の反発があるので、図13の様な反発現象が発生し、短時間の間にONとOFFを何回か繰り返してから最終的にONになります。

押しボタンスイッチのボタンから指を離して、OFFにする場合は、ボタンを押す場合の様に電極同士が激しくぶつかり合う訳ではありませんが、電極が離れる過程で接触状態が不安定になるため、やはり短時間の間にONとOFFを何回か繰り返してから、最終的にOFFになります。

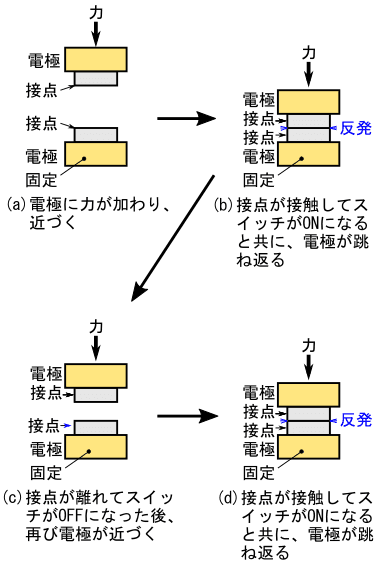

図14に示す様な、プルアップ抵抗を押しボタンスイッチでGNDに接続して、抵抗とGNDの中点の電圧からスイッチの状態を読み取る回路においては、図15に示す様に、出力波形にバウンスの影響が観測されます。

VCCは、電源VCCの電圧を表しています。

本来バウンスとは、スイッチがONからOFFに切り替わる瞬間やOFFからONに切り替わる瞬間に発生する、一時的なONとOFFの繰り返しの現象を指すのですが、その時にスイッチの状態を読み取る回路に現れる出力電圧のバタつきの事も、バウンスと呼ぶ事がしばしばあります。

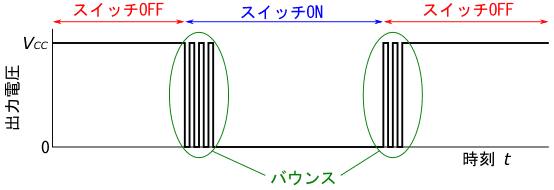

一方で、チャタリング(chattering)というのは、接点が閉じてスイッチがONになっている時に、スイッチに大きな外力が加わる事により、一瞬接点が開いてしまう(スイッチがOFFになってしまう)現象をいいます。

図14の回路でスイッチがONになっている間に、回路に衝撃が加わってチャタリングを起こすと、図16の様な波形になります。

VCCは、電源VCCの電圧を表しています。

本来チャタリングとは、スイッチに衝撃が加えられる事で、ONになっているはずのスイッチが一時的にOFFになる現象を指すのですが、その時にスイッチの状態を読み取る回路に現れる出力電圧のバタつきの事も、チャタリングと呼ぶ事がしばしばあります。

実はバウンスという言葉とチャタリングという言葉は、しばしば混同されて使用されています。このページでは、スイッチのON・OFFの状態が切り替わる時に発生する現象をバウンスと呼んでおり、スイッチがONの時に外力によって発生する現象をチャタリングと呼んでいますが、スイッチのON・OFFの状態が切り替わる時に発生する現象をチャタリングと呼ぶ事もしばしばあります。(筆者も、スイッチのON・OFFの状態が切り替わる時に発生する現象をチャタリングと呼ぶ事がよくあります)

ただ、JIS C5442-1996の「制御用小形電磁リレーの試験方法」では、スイッチのON・OFFの状態が切り替わる時に発生する現象をバウンスと定義し、スイッチがONの時に外力によって発生する現象をチャタリングと定義しています。

このページは、前述のJISの定義に従ってバウンスとチャタリングを説明していますが、このバウンスとチャタリングの区別は、電子工業の分野で広く受け入れられている訳ではない事に注意が必要です。

バウンスやチャタリングが発生すれば、スイッチを一度だけしかONにしていないのに何度もONにしたと回路に判定されたり、スイッチをONにし続けているのに一瞬OFFにしたと回路に判定されたりと、不具合が発生します。

もし、スイッチを操作してから回路が反応するまでの時間が少し(例えば0.1秒程度)遅れていいのであれば、バウンスやチャタリングの対策ができます。

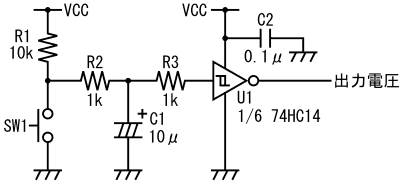

図17に、反転型シュミットトリガ回路である74HC14を用いたバウンス・チャタリング除去回路の例を示します。

電源電圧が2~6Vの範囲で、この回路が動作します。

C2は、電源VCCの電圧を安定させるためのパスコンです。

R3は、電源を切った時にU1の入力端子にC1にた溜まった電荷が流入してU1が故障しない様にするための、電流制御抵抗です。R3は回路の動作には寄与しません。R3がどういう働きをするかは、後のコラムで説明します。

74HC14のIC1個の中に、反転型シュミットトリガ回路が6個入っていますが、この回路では反転型シュミットトリガ回路を1個しか使わないために、1/6 74HC14という表記になっています。もし他の5つの反転型シュミットトリガ回路を使用しないならば、それらの入力端子はGNDまたはVCCに接続してください。

いきなり図17の回路全体の動作を考察するのは難しいので、図17の回路からR1、SW1、R2、およびC1の4つの部品を取り出した図18の回路について、まず考えてみます。

図18の回路においてSW1がOFFの場合は、図19の様に、コンデンサC1をR1とR2の抵抗を介してVCCにつなぐ、充電回路になります。C1は、時定数C1(R1+R2)で充電されます。ただし、C1はコンデンサC1の静電容量、R1とR2は、抵抗R1と抵抗R2のそれぞれ抵抗値です。

図18の回路においてSW1がONの場合は、図20の様に、コンデンサC1の両端子をR2を介してショートする、放電回路となります。C1は、時定数C1R2で放電されます。

ここで、図18の回路のSW1をOFF→ON→OFFと切り替えて、スイッチの切り替え時にバウンスが発生した場合に、コンデンサC1の両端電圧vCがどのような波形になるかを考えてみます。

結論から言うと、vCの波形は図21の様になります。

スイッチSW1をONにすると、コンデンサC1が放電されてvCは低下し、SW1をOFFにすると、C1が充電されてvCは上昇しますが、放電や充電は抵抗を介してゆっくりと進むので、図21の様ななだらかな波形になります。バウンスが発生している所は波形が上下するものの、コンデンサのない図14の回路の出力波形(図15)の様に、0VとVCCの間を振動する事はなくなり、小刻みな振動となります。

さらに細かい事に注目すると、放電時の時定数C1R2は充電時の時定数C1(R1+R2)より小さいため、放電は比較的短時間に進むのに対して、充電は放電より時間がかかります。

図17のバウンス・チャタリング除去回路では、図21の波形を74HC14に入力する事になるため、74HC14の出力電圧は、図22の下側のグラフの様になります。

ここでVTLHは、Lと認識されていたシュミットトリガ回路の低い入力電圧が徐々に高くなって、Hと認識される様になる時の閾値です。また、VTHLは、Hと認識されていたシュミットトリガ回路の高い入力電圧が徐々に低くなって、Lと認識される様になる時の閾値です。

vCが振動的に減少や増加しても、その振動の幅が74HC14のヒステリシス(VTLH-VTHL)より小さければ、その振動が出力電圧に出てくる事はありません。この様にして、バウンスの振動波形を取り除く事ができます。

時定数を大きくすれば、バウンスが持続する時間が長いスイッチに対応する事ができるようになりますが、スイッチ操作をしてから出力電圧にその影響が現れるまでの時間も長くなります。あまり時定数を長くすると、プッシュスイッチを連打した場合に、キー操作を取りこぼす可能性があります。

一方で、時定数を短くすれば、バウンスが持続する時間が短いスイッチを使わないとバウンスの影響を完全に除去できなくなりますが、キー操作が速やかに出力電圧に反映される様になります。

厳密にいうと、スイッチのバウンス持続時間によって、最適な時定数があるのですが、筆者の経験上、充電時の時定数C1(R1+R2)を100ms(0.1秒)程度に設定すれば、ほとんどのスイッチに対応できます。実際に図17の回路では、充電時の時定数は110msに設定しています。

参考:シューティングゲームなど、応答の高速性を求められる用途の場合は、バウンス時間の短いスイッチを使い、時定数を短く設定する方がいいでしょう。

次に、図18の回路における、チャタリング発生時のvCの変化について考えます。

スイッチS1がONになっている時に、スイッチに外力が加わってチャタリングが発生すると、瞬間的にS1がOFFになってしまうために、vCは図23の様に変化します。

チャタリングでスイッチが一瞬OFFになるといっても、スイッチがOFFになる時間が極めて短い事や、充電の時定数に比べて放電の時定数が短い事から、チャタリング発生時も、vCはわずかにしか上昇しません。。

図17のバウンス・チャタリング除去回路では、図23の波形を74HC14に入力する事になるため、74HC14の出力電圧は、図24の下側のグラフの様になります。

チャタリング発生時に、vCがVTLHを超える事がなければ、図17の回路の出力はずっとHになり、チャタリングが表面化しません。

なお、バウンスがうまく除去できる様に時定数を決定していれば、チャタリングについても問題なく除去できるでしょう。

ところで、図14の回路ではスイッチがONの時に出力がLになり、図17の回路ではスイッチがONの時に出力がHになります。これらの回路を「スイッチがONになった事を検出する回路」ととらえれば、図14の回路は負論理の回路となり、図17は正論理の回路となります。74HC14は反転型のシュミットトリガ回路なので、この様に論理の反転が生じます。

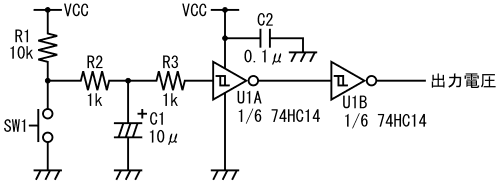

もしバウンスやチャタリングの対策をした波形を負論理で取り出したいなら、図25の様に、図17の回路の後にもう1つ74HC14による反転シュミットトリガ回路を追加したり、図26の様にR1とSW1の配置を交換すればいいでしょう。

図17の回路の後段に追加するのは、反転シュミットトリガ回路でなくても、74HC04の様なヒステリシスのないNOT回路で構いません。しかし、74HC14の反転シュミットトリガ回路が余っているなら、それを使って部品の種類を増やさない方が、コストが低下します。

図17の回路からR2を取り除いた図27の回路が、バウンスやチャタリングの除去に使われている事例を時々見かけます。

図27の回路の場合、コンデンサC1の充電時の時定数はR1C1で、C1の放電時の時定数は0となります。つまり、S1がONになると、放電が瞬時に終わります。

この場合、スイッチS1をOFF→ON→OFFの順に切り替えると、C1の両端電圧vCと出力電圧の波形は図28の様になります。

この波形を見ると、バウンスの影響が出力電圧に表れていないので、図27の回路は良好に動作しそうな気がします。そして、実際に図27の様な回路を試作すると、問題なく動作する場合が多いのです。

さらにいうなら、放電が瞬時に行われる様になった影響で、vCが74HC14の閾値付近で振動する事がなくなりました。ヒステリシスのある74HC14ではなく、ヒステリシスのない74HC04でも動作しそうな気もしてきます。

しかし、図27の回路には落とし穴があります。

R2を取り除いて0Ωにすると、SW1をONにした瞬間に、理論的には無限大の放電電流が流れます。実際には、SW1の接点の接触抵抗や、配線の抵抗や、C1の等価直列抵抗などにより、放電電流は無限大にはならず、有限の値になるのですが、かなり大きな電流が流れる事には違いありません。そうなると、放電電流がSW1の定格電流を超えてしまいます。

たとえ試作回路がうまく動作しても、SW1に過大な電流を繰り返し流す事により、接点の劣化が徐々に進みます。そのため、製品を製造して出荷検査にパスしても、製品が市場に出た後で、不具合を起こしたり、寿命が想定より短くなったりするのです。

また、図28のvCの様に、緩やかに変化する波形を、ヒステリシスのないCMOSのロジックIC(74HC04など)に入力すると、貫通電流が流れて消費電流が増えたり故障したりするため、シュミットトリガ入力のロジックIC(74HC14など)を使う必要があります。

図17の回路からR3を取り除いた図29の回路が、バウンスやチャタリングの除去に使われている事例を時々見かけます。

この回路は、電源を入れている間は正常に動作し続けます。しかし、回路の電源がOFFになった時に、壊れる可能性があります。

この事を理解するには、CMOSロジックICの入力端子に保護ダイオードが付いている事を理解する必要があります。

CMOSロジックICの入力端子には、図30の様に、PチャネルとNチャネルのMOS-FETのゲート端子が接続されています。

例として、構造の簡単なNOT回路を挙げましたが、他のロジックICでも、入力端子にはPチャネルとNチャネルの2種類のMOS-FETのゲート端子のみが接続されています。(ただし入力端子につながっているゲート端子は2つとは限りません)

ゲート端子はドレイン端子とソース端子の間の半導体が形成するチャネルと、薄い絶縁層で絶縁されています。

そのため、ゲート・ソース間、あるいはゲート・ドレイン間のインピーダンスは極めて高く、入力端子が静電気を帯びても、溜まった電荷の逃げ場所がありません。

また、ゲートとチャネル間の絶縁層は極めて薄いため、ゲートに少し高い電圧がかかるだけで、絶縁層が絶縁破壊を起こしてしまいます。

この様に、CMOSロジックICは、原理的に、静電気にとても弱いのです。昔のCMOSロジックICは、静電気を帯びた手で触れたら、簡単に壊れてしまいました。

これでは非常に使いにくいため、現在のCMOSロジックICの入力端子には、図31の様に入力保護用のダイオードが付いています。

回路の動作中は、電源VCCには正の電圧VCCが加わっており、また入力端子には0~VCCの範囲の電圧が入力されています。この場合、2つの入力保護ダイオードD1とD2は、逆バイアスになっており、導通しません。

しかし、図32の様に、静電気などにより正のパルス状の大きな過電圧が掛かった場合は、入力端子の電圧がVCCを超え、D1が順バイアスになって導通します。その事により、正のパルス状の過電圧信号は、D1を介して、VCC電源に逃がされます。

仮に、静電気を帯びた手で入力端子を触った事により過大信号が発生したのなら、電流が流れだした瞬間に皮膚抵抗で電圧降下が生じ、入力電圧が急低下します。この様にして、入力端子の電圧がVCCを大きく超えない様にD1により制限され、MOS-FETが絶縁破壊してしまう事を防ぐ事ができます。

また、図33の様に、静電気などにより負のパルス状の大きな過電圧が掛かった場合は、入力端子の電圧が負の値になり、D2が順バイアスになって導通します。その事により、負のパルス状の過電圧信号は、D2を介して、GNDに逃がされます。

74HC14の入力端子にも、図31の様な入力保護ダイオードが付いている事を考慮して、図29の回路の電源がOFFになった場合の挙動を考えてみましょう。

図29の回路が、SW1がOFFのまま、十分な時間動作すると、C1は、両端電圧vCが電源電圧VCCになるまで満充電されます。この状態で電源がOFFになると、電源電圧が低下して、vCが電源電圧より高い状態になります。(図34参照)

この時、74HC14に内蔵されている入力保護ダイオードD1が導通し、D1を通り抜けて電源ライン(VCC)に放電電流i1が流れます。放電ルートは、これ以外にも、R1とR2を介して電源ラインに抜けるルートがあります。このR1とR2を通るルートの放電電流をi2とします。

コンデンサC1の放電電流iCは、キルヒホッフの電流則より式(1)の様に求まります。

また、C1の容量をC1、時刻をtとすると、放電電流iCは式(2)の様に求まります。

D1が導通している事を考えると、vCは、電源がOFFになって以降の電源電圧vCC(OFF)から、次の様に求まります。

式(3)の両辺をtで微分すると、式(4)が求まります。

式(4)を式(2)に代入すると、最終的に式(5)が求まります。

つまり、C1の容量が大きいほど放電電流が大きくなり、また電源をOFFにして以降の電源電圧の低下が急激であるほど放電電流が大きくなります。

ここで、図35の様に、同一基板内の図29以外の回路を、C1の負荷として考えてみます。

C1の放電電流iCは、いったんi1とi2に分かれてから電源ラインに流れ込みますが、この電流はどこかで消費される必要があります。74HC14は、貫通電流が流れない条件で使っている限り、非常に低消費電流のICなので、U1自身はiCをほとんど消費しません。(気温が25℃の時の74HC14消費電流は1μA以下)

そうだとすれば、iCは、同一基板内の図29以外の部分で消費される事になります。図35の右の長方形の記号は、図29以外の部分の負荷を表しています。

もし、この長方形で表わされた負荷が重く、電流をよく流すなら、iCが大きな値になり、電源電圧が急低下します。

一方でi2は、D1が導通している限りは負荷の重さにあまり依存せず、式(6)で決まります。

参考:R1=10[kΩ]、R2=1[kΩ]として計算すると、i2≒64[μA]と、非常に小さな値になります。

よって、負荷が重くなって増えるのはD1を通るi1の方になります。

あまり負荷が重くなると、i1がD1に流してよい電流の上限値を超えてしまいます。そしてD1に過電流を流すと、74HC14が故障する可能性があります。

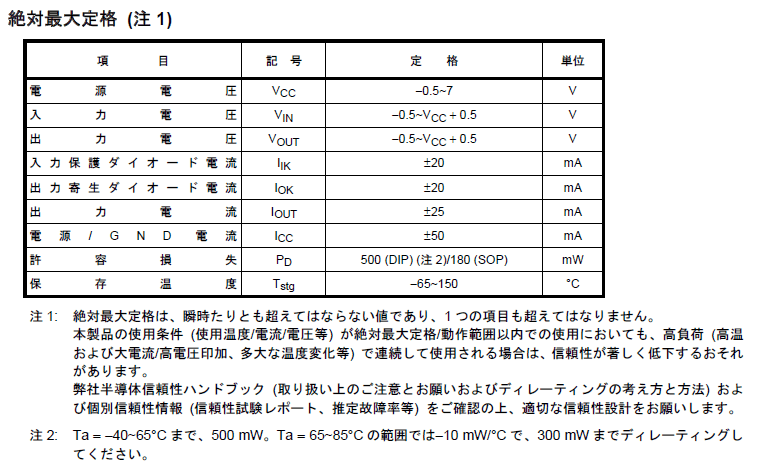

東芝デバイス&ストレージ株式会社製のTC74HC14APのデータシートの、絶対最大定格の項目(図36)を見ると、D1に流してよい電流の最大値は20mAである事が分かります。

i2は約64μAと、20mAに比べて非常に小さい値なので無視する事にすると、負荷に流れる電流iCが20mAを超えてはならない事になります。

以上の議論で分かる様に、D1に流れるC1の放電電流が絶対最大定格を超えるかどうかは、図29と同一基板に載っている回路がどの程度電流を消費するかによって決まります。よって、図29の回路だけを試作して動作試験しても問題が発生しないのに、実際の回路に図29の回路を組み込むと74HC14が壊れるというような、一見不可解な現象も起こり得ます。

この様な不可解な現象を避けるには、C1と74HC14の間に1kΩ程度の抵抗(R3)を挿入して、図17の回路にする必要があります。

図17の回路では、R3が74HC14に流れ込む電流を制限するため、VCC電源を上限の6Vに設定しても、6[v]÷1[kΩ]=6[mA]を超える電流がD1に流れる事はありません。絶対最大定格の20mAには、余裕を持って収まります。

注:D1に流れる電流が6mAというのは、D1の順方向電圧降下(0.7Vくらい)やi2を無視して計算していますので、少し過大に見積もっています。

R1の抵抗値は、680Ωでも1.5kΩでも構わないのですが、極端に大きな抵抗値(例えば100kΩ)に設定すると、74HC14の入力端子の寄生容量(TC74HC14APの場合は、典型値で5pF)とR3により構成される時定数や、74HC14の入力端子のインピーダンスの上昇などが回路動作に悪影響を及ぼす事があります。

図29の回路に限らず、図37の様に、CMOSロジックICの入力端子とGNDに数百pF以上のコンデンサやがつながる回路や、図38の様に、CMOSロジックICの入力端子とVCCに数百pF以上のコンデンサやがつながる回路を使う必要がある場合は、図39や図40の様に、CMOSロジックICの入力端子に1kΩ程度の電流制限抵抗を入れる事を習慣づけるといいでしょう。

参考:図40の回路は、電源をONにした直後と、電源をOFFにした直後を除くと、図39の回路と同様に動作します。よって、電源をONした直後にリセットパルスを発生する回路(パワーオンリセット回路)の様な、電源操作時の挙動を問題にする回路でなければ、図39の回路に統一してしまうといいでしょう。

なお、図17の回路において、74VHC14や74AHC14などの、電源電圧を超える入力電圧を許容するシュミットトリガ入力のインバータを使用する場合は、R3を省略しても、このコラムで説明した様な問題は発生しません。

次のページでは、反転型シュミットトリガ回路を用いた方形波発振回路について説明します。